ロードマップでわかる!当世プロセッサー事情 第659回

ISSCC 2022で明らかになったZen 3コアと3D V-Cacheの詳細 AMD CPUロードマップ

2022年03月21日 12時00分更新

追加の64MBをどのように接続しているか?

32MBのダイを2つ重ねていると考えるのが妥当

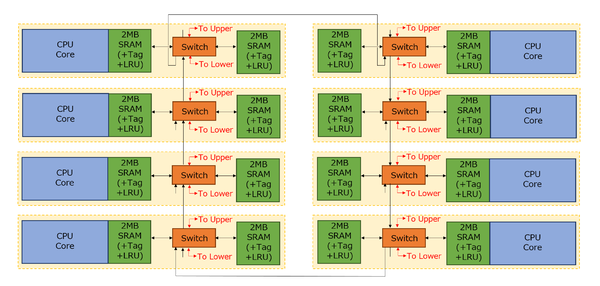

ところで、ここまでの資料でもAMDは「どういうふうに追加の64MBを接続しているのか?」を説明していない。ただヒントはあって、例えば前ページの最初の画像(6つ前の画像)で、TSVをまたぐ通信も32Bytes/サイクルの双方向が、しかも8本あることが示されてる。それと2ページ前の最後の画像(7つ前の画像)で、なぜこれだけの構成にわざわざスイッチとリピーターを噛ます必要があるのか? を考えると、なんとなく答えがわかった気がする。

ここからは筆者の推定である。おそらくであるが、SW0/SW1というスイッチは、もう2本の入出力が可能である。現在SW0/SW1は以下があると説明されている。

- 上方向のスライスへの接続(RPT0経由で上方向へ)

- 下方向のスライスへの接続(下からの矢印)

- 横方向のスライスへの接続(バッファ経由で横方向の矢印)

- SRAMとの接続(7つ前の画像からは省かれている)

これに加えて以下があると考えられる。

- Upper(上に載せたダイへの接続)

- Lower(下にあるダイへの接続)

いずれのリンクも32Bytes/サイクルである。そしてUpper/LowerはTSVに接続される形になっている。もちろんベース・ダイにはLowerはないから、ベース・ダイのLower側は未使用だし、逆にトップ・ダイのUpperも未使用になっているとは思うが。

これを横から見たのが、下図である。

ここでトップ/ミドルの2つのダイが載っている理由は連載618回で説明した通りだ。だいたいベース・ダイが41mm2のエリアサイズで32MBの容量のSRAMなのに、トップ・ダイが同じ41mm2で64MB容量のSRAMを構築するのは、普通に考えたら無理である。となると、32MBのダイを2つ重ねていると考えるのが妥当だろう。

ちなみにこのトップ・ダイ/ミドル・ダイでもリングバッファを構成しているかどうかは不明である。案外トップ/ミドル・ダイではUpper/Lowerのリンクだけが生きている可能性もある。

こういう構成ならシームレスに容量を増やしやすいし、また第618回の最後で触れたように、開発段階で1/2/4スタックの構成があったとしても不思議ではない。筆者の推定が正しいかどうかは現時点では判断できないが、少なくともこの方式は現在AMDが3D V-Cacheの特徴として示している諸々の項目に合致していると考えられる。

現時点で1つ考えられるこの方式の弱点は、モノリシック構成のダイに比べて熱的に弱そうなことだ。Ryzen 7 5800X3Dの発表記事でも触れているが、Ryzen 7 5800X3Dは倍率ロックになることを示唆しており、しかも動作周波数はやや下がっている。

倍率アンロックでオーバークロック動作をすると当然発熱が増えるが、現時点で3Dスタッキングを利用したチップがどの程度熱に強いか(別の言い方をすれば、どの程度の熱に起因するパッケージの歪に、3Dスタッキングは耐えられるのか)は量産チップでは未知数である。

ただ普通に考えると、ベース・ダイはそれなりに発熱が大きい(なにせCPUコアがある)のに対し、トップ・ダイ/ミドル・ダイはSRAMだけなので発熱は最小である。TSV経由で熱はベース・ダイ→トップ・ダイに移動するから長期間で見れば同じ温度になるだろうが、短期的にはトップ・ダイとベース・ダイで温度が完全に一致しない時間の方が多いだろう。

こうした状況では熱膨張率が同じであっても温度の差により寸法が変わってしまうことになる。C4 Bumpなどでは接触面積も大きいので多少の歪みはカバーできるのだが、Hybrid Bumpではなにしろ9μm間隔で接続面が並ぶわけで、歪みの影響は当然大きくなる。

動作周波数をやや下げるとともに、倍率ロックをかけたというのは、フル駆動にすると熱的に耐えられなくなり、接続部が外れてしまう可能性があるからではないか? と筆者は考える。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ