ロードマップでわかる!当世プロセッサー事情 第659回

ISSCC 2022で明らかになったZen 3コアと3D V-Cacheの詳細 AMD CPUロードマップ

2022年03月21日 12時00分更新

3D V-Cacheの詳細をAMDが公開

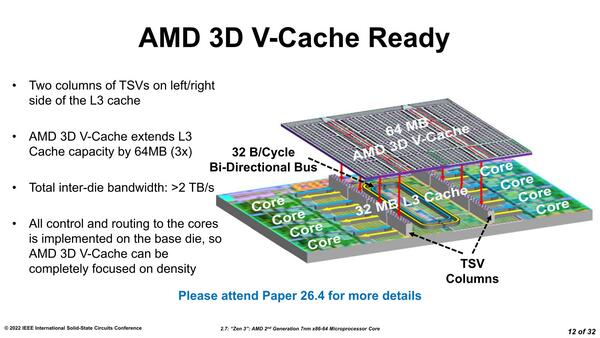

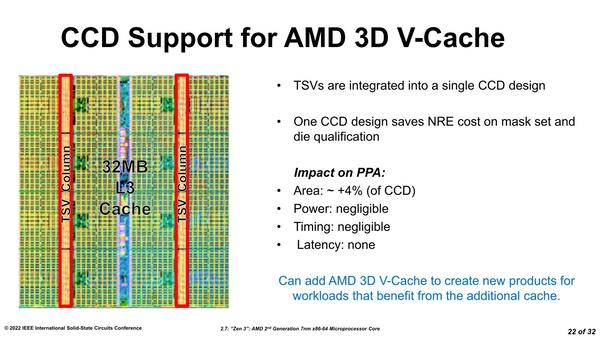

さてそのL3だが、当初から3D V-Cacheの実装が想定されていたようである。このあたりの話は連載651回でも説明しているが、これはTech Insightsによる分析である。

今回はAMD自身により、この3D V-Cache周りの説明があったのでもう少し説明したい。まず実際のTSVの位置配置であるが、3次キャッシュのど真ん中という位置に見える。

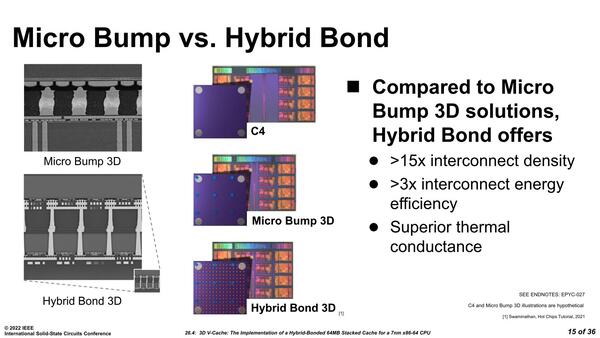

接続方法であるが、SoIC-F2Bを利用して接続しているらしいということは連載618回で説明した。今回はこれがダイの断面撮影付きで紹介された。

右側はわかり難いが、Hybrid Bond 3D→MicroBump 3D→C4で、ダイがどんどん大きくなっていることがわかる。要するに配線密度を高めようとするとMicroBumpでも足りず、Hybrid Bondが必要というわけだ

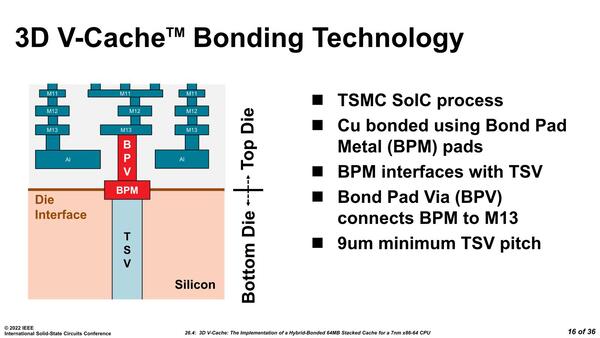

こちらのもう少し詳細な説明が下の画像だ。

以前のTech Insightの資料ではTSVが9μmピッチとされていたが、これが再確認された格好だ

トップ・ダイ、つまり3D V-Cacheの方は配線層が14層(一番下だけがアルミ、その上はすべて銅配線)で、やはりTSMCのN7で製造されるとしている。2つのダイの間の接続はBPM(Bond Pad Metal)と呼ばれるものだが、この材質がなにかについては一切説明がない。BPMは以前TSMCがSoIC-Bondと呼んでいたものであろうと思われるが、単純に銅なのかあるいはなにか他のものか、現時点ではよくわからない。

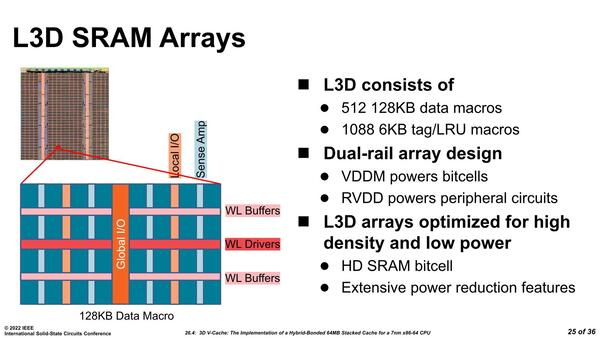

Tag RAMとLRU(Least Recently Used:キャッシュフルの際に、どこをメモリーに追い出すかを決めるアルゴリズムの1つ)用に1088個の6KBブロックがあるとされる。おそらくTagに1024個、LRU用に64個と思われる

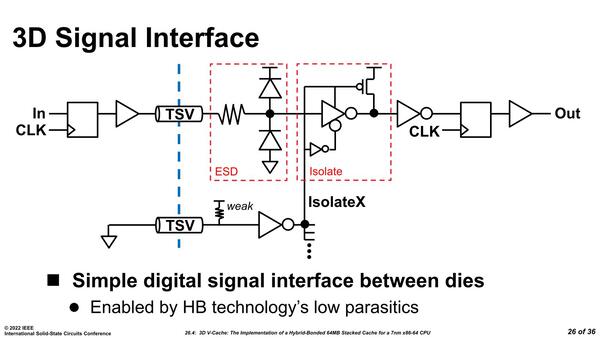

SRAMの構造は、128KBのSRAMブロックを512個集積したとしており、スライスの容量はおそらく4MBのままと思われるので、1スライスあたり32ブロックから構成される。一方、信号レベルでのTSVをまたいだ際の配慮だが、さすがに信号をそのまま接続するというのは危険だったためか、ESD(Electro-Static Discharge:静電気放電)防止用のクランプ回路と、その後で信号を正規化するアイソレーション回路は入っているが、基本はその程度で済んでいるようだ。

これがインフィニティー・ファブリックやHBM2、あるいは最近話題のUCIeなどでは、きちんとPHYを用意する必要があるので、それに比べると多少配慮はしているものの、基本信号線をそのままつないでいる感じに近い

ただその前後にバッファが入り、クロックで同期しているあたり、どうしても1サイクル分のレイテンシーが増えることは避けられないようだ。そうは言ってもたかだか1サイクル程度のレイテンシー増加で容量が64MB増えれば、十分ペイすると考えていいだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ