ロードマップでわかる!当世プロセッサー事情 第648回

VIA C3を開発したCentaurをインテルが買収、もとはMIPSだったArchiTekのRISC-Vコア

2022年01月03日 12時00分更新

もとはMIPSだったArchiTekのRISC-Vコア

連載639回でArchiTekのAiOnIcプロセッサーを紹介したが、このチップの中でHigh Performance AIに利用されているRISC-Vコアの詳細は原稿執筆時点では不明であった。

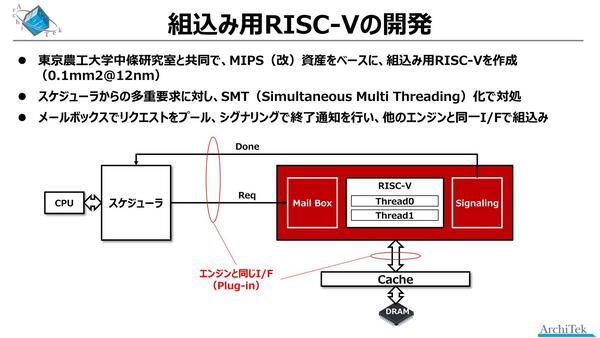

ところが今年11月に横浜で行われたRISC-V Days Tokyo 2021 AutumnでArchiTekも講演しており、ここでRISC-Vコアの詳細が明らかにされたので補足しておきたい。まずコアそのものであるが、ベースとなったのはMIPS32コアで、これをRISC-Vに作り替えたもの、というなかなかおもしろいものだった。

東京農工大 中條研究室の中條拓伯准教授は国内大学機関でRISC-Vを牽引する1人でもあり、最近ではヘネパタ本の第6版(RISC-Vバージョン)の訳者のお一人でもある。それにしても「MIPS(改)」というのはなんだったのか気になるところだ

実はMIPS自体が現在RISC-Vへの対応を進めており、次世代MIPSコアはMIPSとRISC-Vの両対応になることが昨年11月に発表されている。よって、既存のMIPSコアがなにかしらあるのであれば、これをRISC-V対応にするのは容易だったと思われる。

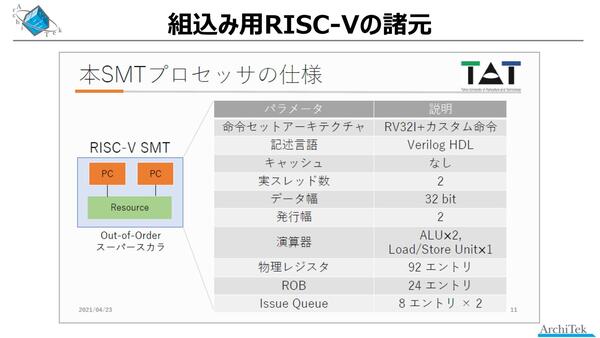

ただSMTの目的はメモリーアクセスのレイテンシー遮蔽ではなく、High Performance AIエンジンからの多重リクエストに対して迅速に対応するため、というのは少し意外であった。内部構成はアウト・オブ・オーダーではあるが、同時2命令発行と比較的小規模なもので、また命令セットはFPUなどを一切含まないRV32I+独自命令という構成であった。

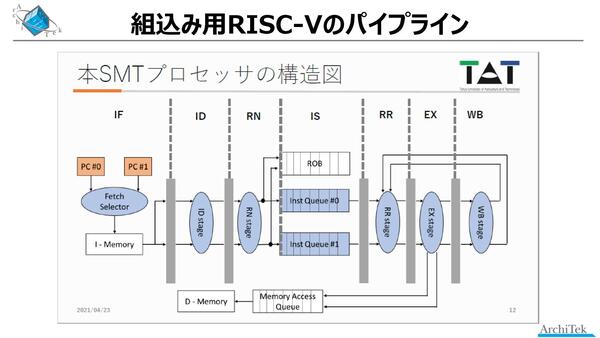

確かにここまで割り切れば、12nmプロセスでエリアサイズ0.1mm2というのも納得である。パイプラインは7段であるが、アウト・オブ・オーダーを実装しているにしてはシンプルな構成である。

またVector Unitも搭載されておらず、その意味ではデータ処理「以外」を受け持つことが明白な構成である。

こうした組み込みであれば64bitアドレスも不要ということで、RV32Iとなっている。RV32Iは純粋に32bitの整数演算命令の基本「だけ」である。したがってALUもかなりシンプルに実装できたと思われる

連載639回では「これはSMTに対応したRISC-Vコア(おそらくこちらもRV32系だろう)にVector Extensionを付けたコアが実装されており、このVector Extensionをブン廻すことで対応する形だ」と書いたが、RV32はともかくVector Extensionを使うような作業はRISC-Vコアにはさせない、という形の割り切りになっていることが明らかである。

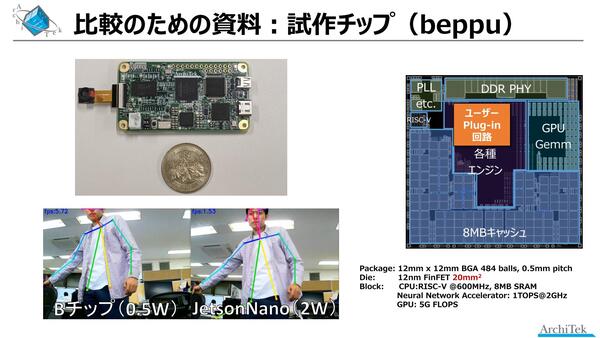

ちなみに試作のbeppuチップが下の画像だ。beppuで動き解析を行なうと0.5Wで5.72fpsを実現できるが、同じことをNVIDIAのJetson Nanoを使うと2Wでしかも1.53fpsしか性能が出ない、としている。

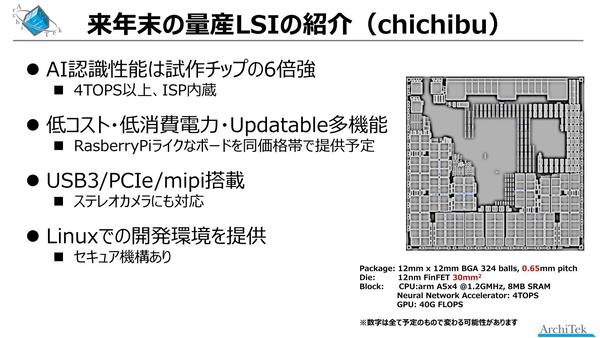

ただbeppuはあくまでも試作で、量産チップのchichibuは2022年末に登場という話であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ