WSEを搭載したCS-1を発表

日本でも受注開始

Hot Chips 31における発表はここで終わりで、実際にネットワークを載せた場合の性能は開示されなかった。これに関しては2019年11月に行われたSC19で発表があるかと思いきや、発表されたのはこのWSEを搭載したCS-1というシステムであった。

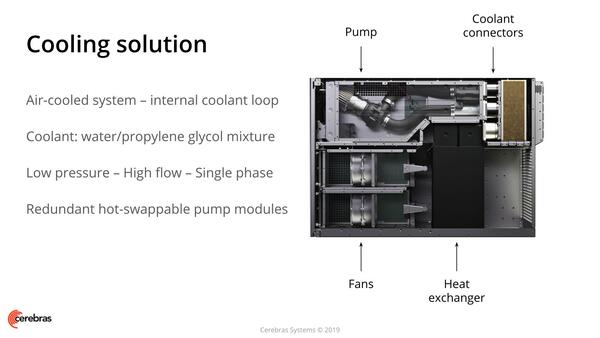

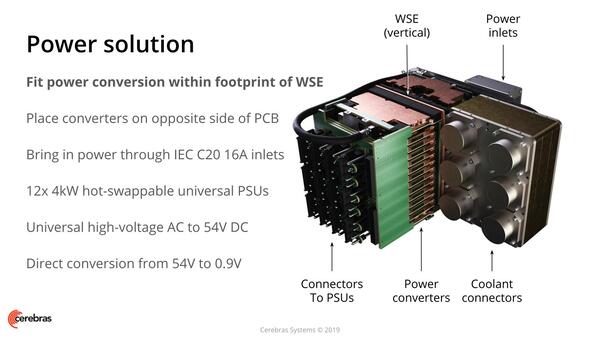

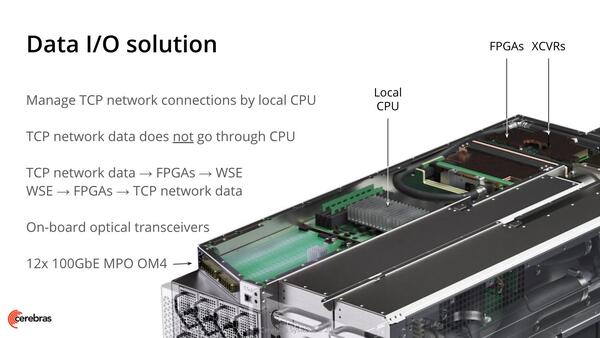

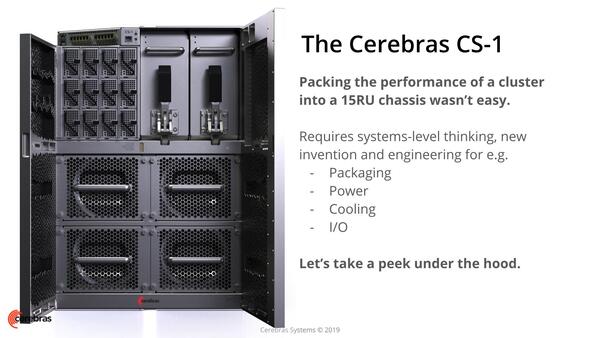

WSEを搭載し「CS-1」。右上の2つ並んでいるのは冷却ポンプ。下の4組は冷却ファン。左上の12個はPSUと思われる。その上の斜めになっている部分には100GbE×12のMPOコネクタと制御用プロセッサー、およびFPGAボードが搭載される

画像の出典は“CS-1 Wafer-Scale Deep Learning System”。(以下、同)

全体の高さは15Uとされる。通常データセンターのラックは42Uなので縦2段積み、たまにある45Uのサイズなら3段積みが可能になる。これを横から見たのが下の写真だ。

CPUはこの写真で言えば右上にある。下半分はほぼ冷却用になっている。そういう意味では液冷といっても、シャーシの外に水冷システムを必要とするものと異なり、PCの簡易水冷の巨大版といった構造になっているのがわかる。そのCPUブロックが下の写真だ。

ちなみにWSEは定格でほぼ15KW(!)ほどの消費電力となっており、おそらくNVIDIAのAmpereと同じくVicorのVRMで供給しているようだ。4KWのPSEが12個も用意されるのも無理ないところである。一番上には制御用CPUと、ネットワーク通信用FPGAが搭載されている。

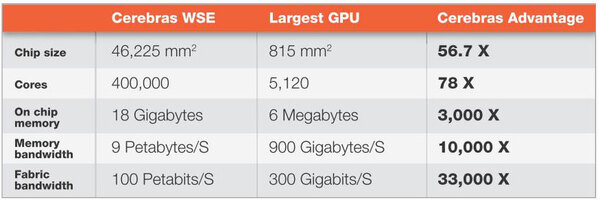

さて、このSC19での発表や、製品紹介でも、繰り返されたのは下の画像の数字だけである。

それにもかかわらず、すでにPSC(Pittsburgh Supercomputing Center)が2台のCS-1の導入を決めたほか、アルゴンヌ国立研究所はこのCS-1を新型コロナウイルスのワクチン開発に転用することを発表するなど、出だしは順調である。

国内でも、昨年12月にTEDがCS-1の代理店契約を締結して受注を開始している。さすがにこうしたパートナーには、実際のモデルを動かした場合の性能が開示されているのだと思いたいが、いまだに具体的な性能が出てきていないというのはやや怪しい感じはある。

また、先ほど開発費を加味するとコスト的にはWSEの方が安くなるという議論をしたが、運用コスト(主に電気代)を考えた場合、長期的にWSEの方が安くなるのかどうか、正直よくわからない。理由は、いまだに性能が開示されていないので、性能あたりの消費電力コストの試算ができないからだ。

ただ、同じようにAI学習を目指したWave Computingが見事に立ち往生し、Cerebrasのビジネスが軌道に乗り始めているのを見るに、Wave Computingはぶっ飛び方が足りなかったのかな? と思ったりもする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ