大幅な性能改善に貢献した

チップレット周り

さて次がチップレットの話。Zen 2ではメモリーコントローラーはCPUダイから外れ、I/O チップレット側に移動したという話はすでに説明した通り。

ここでCPUチップレットとI/Oチップレットの間はインフィニティーファブリックで接続されるが、この帯域もまた32Bytes/サイクルである。これはメモリー帯域が32Bytes/サイクルなのでこれにあわせている。

ちなみにここでいうサイクルはCPUの動作周波数ではなく、インフィニティーファブリックの動作周波数になることに注意されたい(上の画像で言うところのfclk)。

さて、この構造はメリットも多い一方で性能面へのインパクトもある。Ryzen ThreadripperでDynamic Local Modeが用意されたのも、複数チップに分散したことに起因するボトルネックを緩和するための方法の1つであるが、Zen 2でもこうした配慮が用意される。

1つはTopology Awareness。たとえばあるコアで新規スレッドを作成したときに、その新規スレッドが別のCCDで動いたりすると、猛烈な量のアクセスが2つのCCDの間で発生してしまう。

これを防ぐため、同一プロセスに属するすべてのスレッドは、同じCOD(同じCCX)で動かすようにするという配慮がされる。これはハードウェア側の問題ではなく、OSのスケジューラーの問題である。

ちなみにこれは単にRyzen 9 3900シリーズのみならず、従来のRyzen系でも有効であり、Ryzen Threadripperでも有効である。

もう1つはClock Selectionである。ACPI 5.1でCPPC(Collaborative Processor Performance Controls)という機能が追加されており、これは2014年頃のCPUから広くサポートされるようになっているが、これを高速化したCPPC2という機能がACPI 6.0から追加になった。

Zen 2ではこのCPPC2をサポートした結果として、従来30ms程度要していたClock Selectionを1~2msまで短縮できたという話である。

ちなみにこの効果であるが、Topology Awarenessで15%の、CPPC2サポートで6%の性能改善が果たされた、としている。

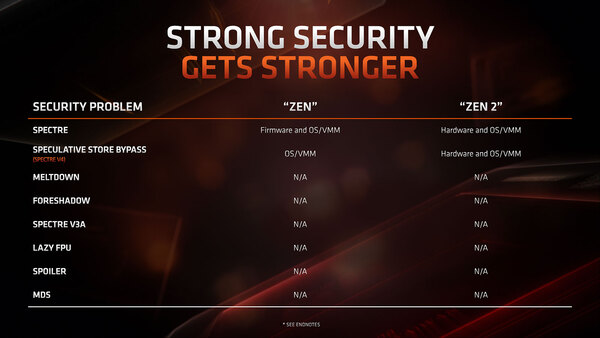

ところで1ページ目のバッファ周りの画像で“Hardware-enhanced Security mitigation”という項目が上がっていたが、具体的な改善項目というのが下の画像だ。

もともとZen系列は、Spectre/Meltdownからスタートした一連の脆弱性に(インテルに比べると)特に対策なしで対応できるという強みがあったが、唯一OS周りの対策が必要だったSpectreに対してハードウェアでの対応を強化したという話である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ