NCUを増やさなかったのは

設計期間短縮のため

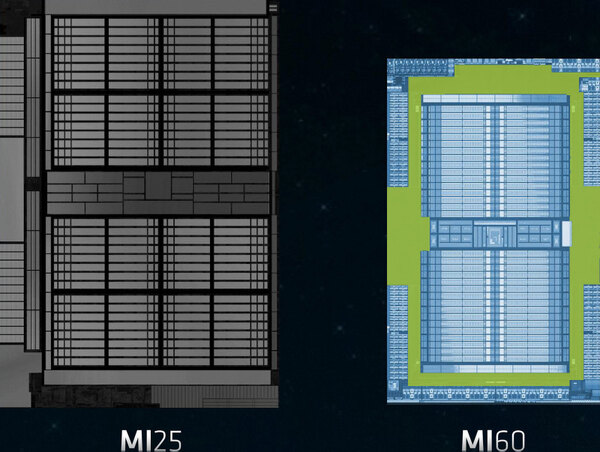

一方横方向だが、下の画像のとおり上辺側はおそらくPCI ExpressのI/FとHDMI/DPなどの画像出力のみである。

こちらは他にいろいろやりようはあったと思うのだが、下辺側に並んでいるのがおそらくインフィニティー・ファブリックのI/Fで、こちらもなにしろ信号速度が速い(連載485回にも書いたが50Gbpsである)から、やはり最短で配線できるようにしておく必要がある。結局この2つがある限り、ダイの外形寸法そのものは変えられなかったと思われる。

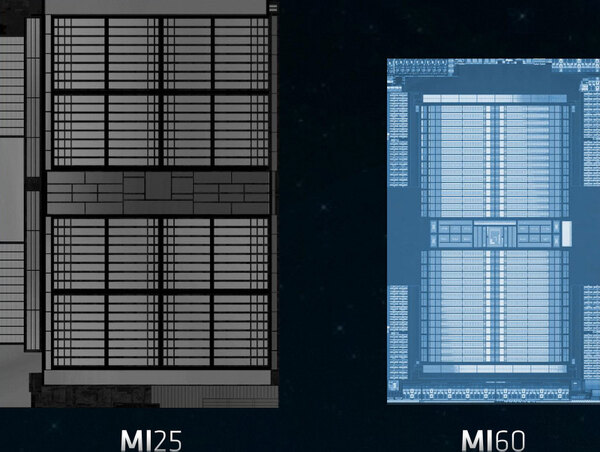

逆に言えば、ダイサイズ的に言えばNUCの数をもっと増やすことも可能だったと思われる。実際下の画像を見る限り、上側にあと6基、下側にあと4基は楽にNCUを増やせたはずで、がんばればトータルで12基ほど増加できたように思われる。

つまり64 NCUではなく76 NCU構成である。これだけで18%ほど増加になるわけで、動作周波数をもっと落としても性能は維持できるし、1800MHzで駆動できればさらに高い性能が獲得できたはずだ。それにもかかわらずこれを行なわなかった理由は、設計期間の短縮であろう。

後述するように、7nm世代の本命はNAVIであり、Vega 20はデータセンター向けなどに特化した、NVIDIAで言えばVoltaにあたる製品である。

実際製造プロセスが大きく変わり(なにしろファウンダリーまで変わった)、最適化技法そのものが異なっているにも関わらずダイ上のレイアウトがほとんど相似形というのは、7nm移行への試験的な意味合いがあったにしても、最適化にあまり時間をかけていなかったためと思われる。

Vega 20ベースのRadeon Instinct MI60/50が2018年中に出荷を開始し、コンシューマー向けのRadeon VIIが今年2月に発売開始できたのは、そうした最適化が十分ではないためだと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ