前回の記事でRS/6000について言及したが、これにつながるIBMのRISCプロセッサーの歴史を説明しよう。

IBMのRISCプロセッサーと言えばPOWERシリーズと、サブセットであるPowerPCシリーズがあることはご存知かと思う(zシリーズを忘れているわけではないが、また別の機会に)。

そのPOWERシリーズの最初の製品であるPOWER1(POWER)と、この後継の話は、連載289回で説明したが、別にいきなりPOWERが湧いて出たわけではない。

RISCプロセッサーの源流にあった

IBM 801プロジェクト

RISCといえば、David Patterson博士とCarlo Séquin博士によるBerkeley RISCやJohn Hennessy博士によるMIPSプロジェクト、あるいはDARPAのVLSIプロジェクトなどが有名であるが、実はいわゆるRISCの源流は、IBMにあった。

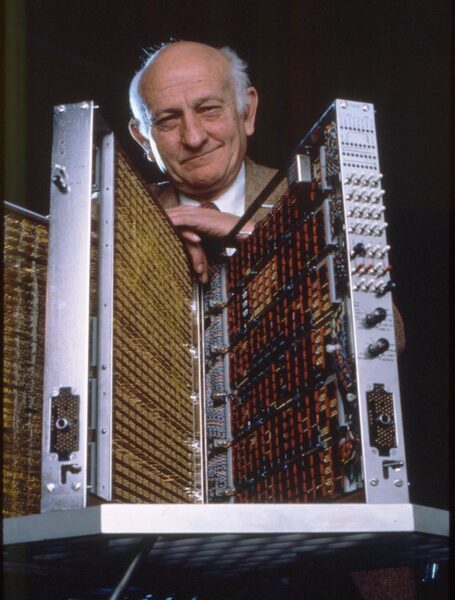

IBM 801プロジェクトというのがそれである。プロジェクトはIBMのThomas J. Watson Research Centerに在籍していたJohn Cocke博士の元、公式には1975年にスタートした。

画像の出典は、IBM 100

Computer History Museumに収録されている“IBM 801 Microprocessor Oral History Panel”を読む限りは、1972年か1973年あたりから、キーパーソンを集めつついろいろ検討を重ねていく作業がぼちぼち始まっていたようで、1975年はこれが正式にプロジェクトとして成立した(どうもその前は非公式に進められていた)らしい。ちなみにこのプロジェクトがIBM 801と呼ばれていたのは、利用していた建物の番号が801だったからだそうだ。

さらに余談だが、IBM 801という製品は、実は1934年に出荷されている。こちらは正式名称は“IBM 801 Bank Proof machine”で、小切手並べかえ、署名と裏書きを行ない、合計を計算する機械だそうである。

画像の出典は、IBM Archives

さすがに40年も前の製品だから、名前が重なっていても問題ないと判断したか、そもそもそんな製品があることを知らなかったのだろう。だいたい、当時これがIBM 801として広く知られるようになるとは当人たちも予測していなかったはずだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ