ダイサイズから割り出す

Zen 2コアの構造

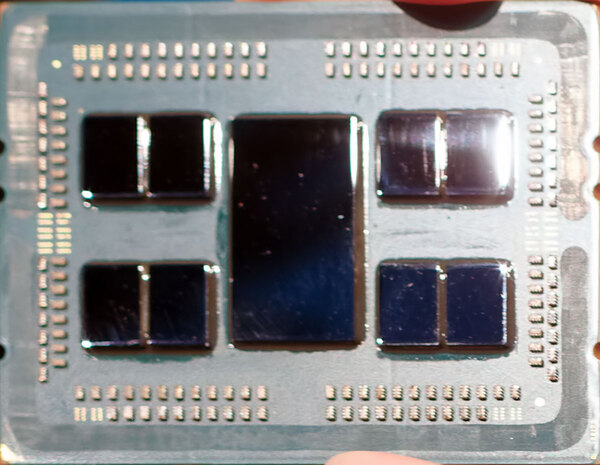

上の画像は基調講演の後で示された7nm EPYCのサンプルだが、パッケージ全体は既存のEPYCと一緒の75×58mmなので、ここからダイサイズを計算すると、以下のようになる。

CPU:7.25mm×10mm=72.5mm2

I/O:15.3mm×27.8mm=425.3mm2

ちなみにZenコアを搭載した既存のダイは213mm2なので、I/OチップはZenのダイのほぼ倍サイズになっている。

理由はインフィニティー・ファブリック・スイッチがかなり容量を食うだろうということと、このI/Oチップにもキャッシュ(4次キャッシュ兼ディレクトリーキャッシュ)が搭載されるためと筆者は予測しているが、さすがにこれをデスクトップやモバイルに持ち込むのは、コスト的にも機能的にも無駄が多い。

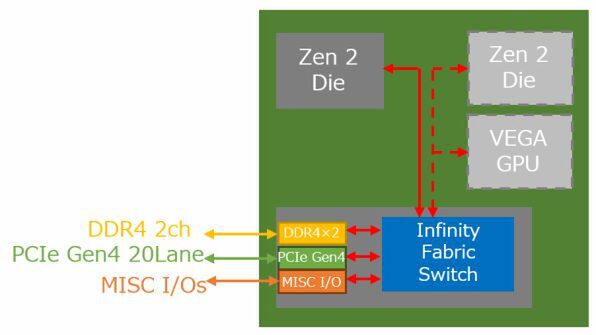

おそらくこのI/Oチップをそのまま使うのはEPYCと次世代のThreadripperのみで、デスクトップ/モバイル向けには別のI/Oチップを用意すると思われるが、それは例えば下図のようなものになるだろう。

最低1つのZen 2ダイのほか、ハイエンド向け(Ryzen 7の上位グレードや、ひょっとするとRyzen 9など)には2ダイ構成もありえるだろう。

逆にメインストリーム向けにはZen 2ダイ+(おそらくはやはり7nmで製造される)VEGAのダイを搭載することでGPU統合が可能になる。ひょっとするとGPUもI/Oチップの中に含むかもしれないが、その場合は14nmないし12nmでの製造になるので、あまり性能が上げられないことになる。

このあたりはもう筆者の推測なのであまり真面目に受け取ってほしくないのだが、ラインナップを自由に作りやすい。図の構成ではインフィニティー・ファブリック・スイッチの規模も小さいし、ディレクトリーキャッシュの必要もないため、4次キャッシュは搭載しないだろう。

そうなると相当I/Oチップのダイサイズは小さくできるはずである。このデスクトップ/モバイル向けのI/Oチップを100mm2以下に抑えられれば、かなり価格競争力は高いだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ