Knights Cornerとの大きな違いは

単体でOSが動作すること

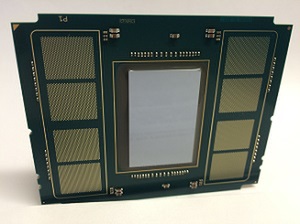

2014年11月にはKnights Landingのダイおよびパッケージ写真が公開された。

これがプレスリリースではなく、開発者向けサイトで公開されたあたりが微妙であるが、ここでさらに以下の情報が公開された。

- コア数は最大72で、コア間が2Dメッシュ構造で接続されている

- トランジスタ数は80億個以上

- AVX-512命令をサポート

大きなポイントとして、単体でOSが動作することも明らかにされている。実はこの、単体でOSが動作するという点が従来のKnights Cornerまでとの大きな違いである。

やや話が遡るが、iPSCあるいはParagonといったマシンは、いずれもすべてのノードでOSが動作していた。iPSC/2は独自のNX/2というOSが、ParagonではSNLが開発したSUNMOSという軽量カーネルのOSがすべてのノードで動作していた。

なぜこのような構造にしたかというと、たくさんあるノードを全部外部のホストから制御していたら、その制御のオーバーヘッドが馬鹿にならないためだ。

したがって、各ノードにそれぞれ軽量なOSを載せ、この上で勝手にプログラムが走るような構造にするほうがトータルとしてのオーバーヘッド削減につながる。

この問題はKnights Cornerでも顕著で、なにしろI/FがPCI Express x16レーンのみなので、ここで60コアの制御などを全部ホストからやろうとすると帯域不足が顕著だった。

ところがKnights Cornerでは個々のプロセッサーにOSが載る構造になっておらず(不可能ではないが、そもそもそれを前提とした構造ではないので非常に効率が悪い)、どうしようもないというジレンマに陥っていた。

Knights Landingではコアそのものの性能を引き上げるとともに、個々のコアで別々のOSが動作することを前提とした構造になったため、このあたりがだいぶ改善されることになった。

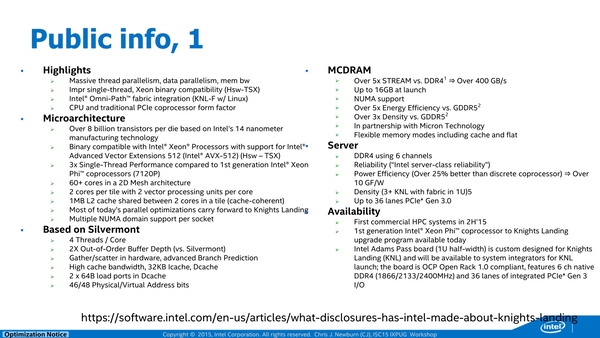

また悪名高かったリングバスを放棄して2Dメッシュを採用したのも性能改善に役立つと思われる。そして、これを利用したサーバーの構成があることも明らかにされた。このあたりをまとめたのが下の画像である。

おもしろいのはKnights Landingでは3D DRAM(左上の画像ではMCDRAM:Multi Channel DRAMと記載されている)の他に、6chのDDR4 I/Fを用意していることで、これとMCDRAMであわせて400GB(384GB DDR4+16GB MCDRAM)のローカルメモリーを利用することも可能な構成になっている。

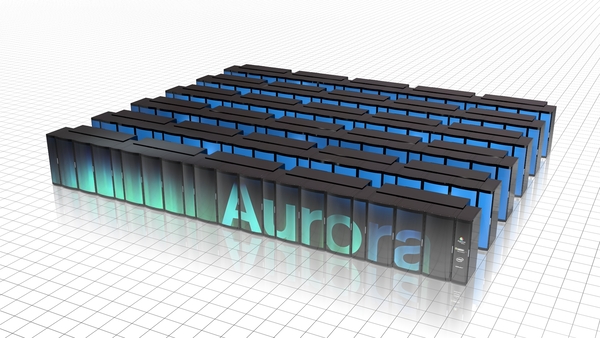

またKnights Landingを最初に利用するのはNERSC (National Energy Research Scientific Computing Center:米エネルギー省の科学技術計算施設) で、2016年中旬までに9300ノード以上を実装したシステムを構築するが、それよりも規模として大きいのはアルゴンヌ国立研究所に設置される予定のAuroraとThetaというシステムだ。

これはオークリッジ国立研究所とアルゴンヌ国立研究所、ローレンス・リバモア国立研究所の共同(Collaboration)ということで、CORALという名称がついているが、2018年までにALCF(Argonne Leadership Computing Facility)に180PFLOPSのシステム(これがAurora)と、2016年中に8.5PFLOPSながら消費電力が1.7MW(これがTheta)を納入する予定になっており、これにKnights Landingが利用される予定となっている(関連リンク)。

→次のページヘ続く (インテルに欠けている要素はなにか?)

この連載の記事

-

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 -

第847回

PC

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手 -

第846回

PC

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ -

第845回

PC

最大256MB共有キャッシュ対応で大規模処理も快適! Cuzcoが実現する高性能・拡張自在なRISC-Vプロセッサーの秘密 -

第844回

PC

耐量子暗号対応でセキュリティ強化! IBMのPower11が叶えた高信頼性と高速AI推論 -

第843回

PC

NVIDIAとインテルの協業発表によりGB10のCPUをx86に置き換えた新世代AIチップが登場する? -

第842回

PC

双方向8Tbps伝送の次世代光インターコネクト! AyarLabsのTeraPHYがもたらす革新的光通信の詳細 - この連載の一覧へ