富士通研究所、4つの『FR-V』プロセッサーコアを1チップに集積したデジタル民生機器向けCPUを発表――世界初の8way VLIW CPUによるクアッドコアCPU

2005年02月07日 09時04分更新

|

|---|

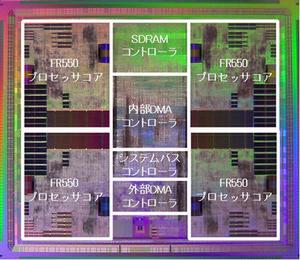

| 発表されたCPU、『FR1000』のダイ写真。4つの『FR550』プロセッサーコアのほかに、DMAコントローラーやメモリーコントローラーを内蔵する |

|

|---|

| 富士通研究所 システムLSI開発研究所 所長代理の山村毅氏 |

(株)富士通研究所は7日、533MHzで動作する『FR550』プロセッサーコアを4個搭載したマルチコアCPUを開発したと発表した。従来のFR550の4倍の性能を発揮し、High Difinition品質のビデオデータのデコードを、ソフトウェアのみで処理できるという。このCPUは米国サンフランシスコで開催されている半導体関連技術の学会“ISSCC 2005”で発表された。日本で行なわれた報道関係者向け説明会では、富士通(株)LSI事業本部 FR-Vソリューション事業部 事業部長の坂本喜則氏と、富士通研究所 システムLSI開発研究所 所長代理の山村毅氏により、同プロセッサーの説明が行なわれた。

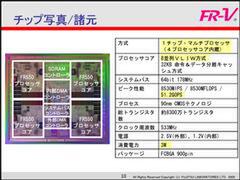

発表されたマルチコアCPUはコード名“FR1000”と呼ばれるCPUで、同社の組み込み用途向けVLIW(※1) プロセッサー“FR-Vファミリー”の『FR550』をベースに開発された。FR550は1クロックで最大8命令/28演算を並列実行可能なVLIWプロセッサーで、32KBの命令キャッシュと32KBのデータキャッシュを内蔵する。FR1000ではFR550のコア部分と、各コアごとに用意された128KBのワークメモリーをそれぞれ4個内蔵している。製造プロセスは90nmプロセスで、トランジスタ数は8300万個、ダイサイズは12×10mm。動作周波数は533MHz。

※1 VLIW Very Long Instruction Wordの略で、1つの命令語の中に並列実行可能な複数の命令をまとめておき、それを並列で実行させる処理方式。一般的には命令語の並べ替えとまとめなどの最適化処理は、プログラムの作成時にコンパイラーで行なう。インテルの“Itanium”や、トランスメタの“Crusoe”などが有名。 |

| |

|---|---|---|

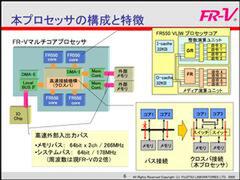

| FR1000のブロックダイアグラム | FR1000の主な仕様 |

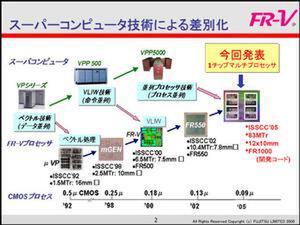

コア自体は従来からあるFR-Vファミリーとの互換性があり、これにコア同士の通信に使う通信ライブラリーを組み合わせることで、FR-V用に作られたプログラムを少ない変更で動作させられる。ワークメモリーは64bitのインターフェースで各コアにつながっており、コアと同じクロック周波数で動作する。各コア同士は高速なクロスバー接続で接続される。FR1000内にはその他に、コア同士を結ぶ内部DMAコントローラー、システムバスにつながる外部DMAコントローラー、DDR SDRAMコントローラー(DDR266 SDRAMに対応)などを内蔵する。もともとFR-Vファミリーは、(株)富士通のスーパーコンピューター“VPPシリーズ”で培われたノウハウを元に開発されたCPUで、VLIWコアやクロスバー接続などに、その技術が応用されているという。

|

|---|

| 富士通のスーパーコンピューター技術の系譜と、それを応用したFR-Vファミリーの系譜 |

またFR1000の特徴として山村氏らは、平均消費電力3Wという消費電力の低さを挙げた。その他にも、プロセッサーを組み込んだ製品の開発期間を短縮する設計手法も同時に開発した。従来の方法では、いったん製造されたプロセッサーを基板上に組み込んでテストを行なうが、その際に基板上の電源ノイズによる動作不良などが起こると、プロセッサーや基板を再製造しなくてはならず、開発期間が長くなっていたという。そこでプロセッサーのレイアウト設計と並行してプリント基板の仮設計を行ない、これらを元に基板製造前に高精度の電源ノイズ解析シミュレーションを行なうことで、動作不良を抑制して開発期間を短縮できるとしている。

|

|---|

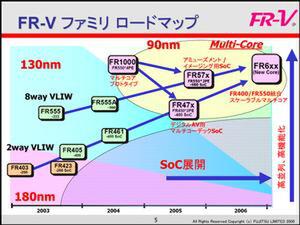

| FR-Vファミリーのロードマップ。8命令並列実行版のFR5xx系列と2命令版のFR4xx系列がある。FR1000はファミリー初の90nmプロセスCPUでもある |

FR1000は4個のプロセッサーコアを533MHzで動作させることで、従来のFR550の4倍(マルチプロセッサー化で3倍+高クロック化による)の性能を達成しているという。ただしFR1000自体はマルチコアCPUのプロトタイプという位置づけで、そのまま製品化されるものではない。実際にデジタル家電などへの採用を目指すのは、FR550のデュアルコア版であるコード名“FR57x”や、2命令並列実行型のVLIWプロセッサーコア“FR461”を2個1チップに搭載するコード名“FR47x”になるとのことだ。内蔵コア数が少なくなるため、FR1000のようにデジタルハイビジョン品質のMPEG-2やH.264/AVCのソフトウェアデコードはできないが、既存のSD解像度のビデオエンコード/デコードには十分対応できるとして、FR57xはアミューズメント機器(たとえばパチンコ用)やデジタルイメージング機器、FR47xはSD解像度のAVデジタル家電や携帯AV機器への応用を目指すとしている。サンプルの出荷時期は、FR47xが今年夏頃、FR57xが秋から年末にかけてを予定している。