米インテル社は11日(現地時間)、ゲート長が30nm(ナノメートル:10億分の1m)と世界最小のCMOSトランジスター技術の開発に成功したとと発表した。この技術を開発した研究者が、米カリフォルニア州サンフランシスコで10日から13日まで開催中のインターナショナル・エレクトロン・デバイセズ・ミーティング(IEDM)において詳細を発表するとしている。

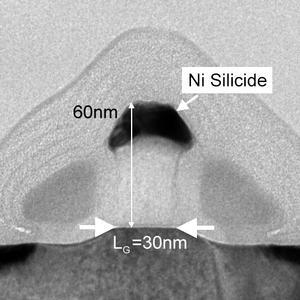

今回実験室で製造されたトランジスターは、ゲート長が30nmで、ゲート酸化膜の厚さが分子3個分にあたる0.8nmであるという。トランジスターは小さいほど高速に動作するが、この試作されたトランジスターは500GHzで動作しており、これは10GHzで動作するプロセッサーに必要な速度を満たしているという。

|

|---|

| 試作されたゲート長30nmのCMOSトランジスターの画像 |

インテルでは現在半導体製造にあたり0.18μmプロセス技術を使用している。今回発表されたような微細なトランジスターの製造には0.07μmプロセス技術が必要というが、同社の半導体製造技術のロードマップでは、2001年に0.13μmプロセス、2003年前後に0.10μmプロセス、2005年前後に0.07μmプロセスに達する計画。順調に開発が進めば2005年前後に、動作周波数10GHz、集積トランジスター数4億個で1V以下の電圧で動作するプロセッサーが登場する見込み。

各半導体製造プロセス技術におけるゲート長の比較(インテルによる)

| 製造プロセス | ゲート長 | ゲート酸化膜の厚み |

| 0.18μm | 130nm | 不明 |

| 0.13μm | 70nm | 1.5nm |

| 0.07μm | 30nm | 0.8nm |