ロードマップでわかる!当世プロセッサー事情 第831回

Intel 18AはTSMCに対抗できるか? RibbonFET/PowerVIAの可能性と限界 インテル CPUロードマップ

2025年07月07日 12時00分更新

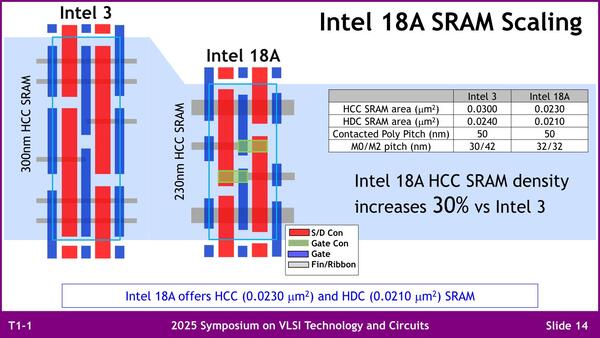

Intel 18AのSRAMはIntel 3と比べて30%以上密度が向上

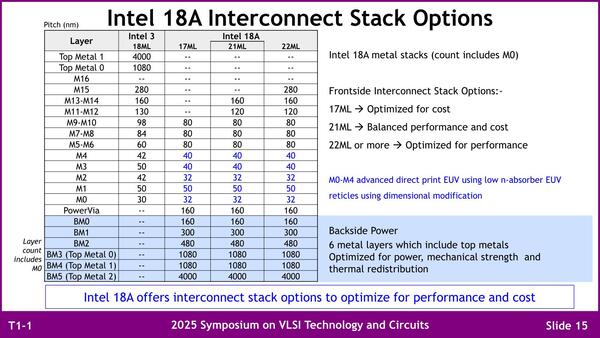

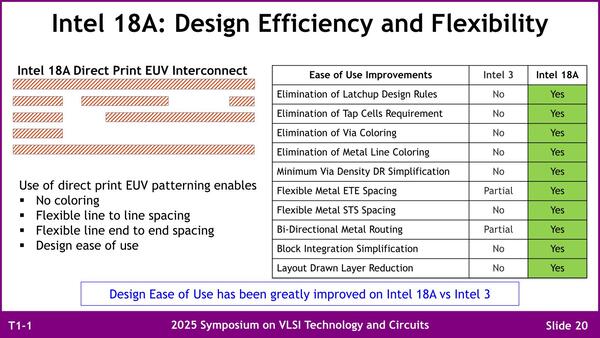

次に配線層の話であるが、Intel 18Aでは"direct print EUV"と呼ばれる技法がM0~M4で採用されたことにより、M0~M4の配線層構築に必要なマスク数と手間が大幅に減少した、としている。

PowerVIAを実装の結果、配線層の層数の合計そのものはやや増えるわけだが、一番トランジスタに近いBM0でも160nmピッチと、配線層のM13-14と同等でかなり太いので、実装のコストは相対的にかなり低いから、製造コスト増加の割合はごくわずかだろう

その配線層のPitchが上の画像だ。Intel 3の時の配線層のPitchと比較すると、そもそもPowerVIAを使う関係で電源供給が裏面に移動しているため、Top Metalがなくなり、代わりにBM0~BM5が追加されている。

Intel 3における配線層と比較した場合、PowerVIAのお陰で多少配線にゆとりがあるためだろうか? Intel 3ではM5~M6が60nmピッチだったのに対し、Intel 18Aでは80nmとずいぶん緩和された。Intel 3ではM5~M6までローカルのインターコネクトに割り当てていたのが、Intel 18AではM4まででカバーできるようになったということかもしれない。

そのIntel 3では連載784回で説明したように、M0~M6までがeCU(※)を採用していたが、今回の配線層に関してはこの材質の説明がない。

ただ80nm Pitchでは別にeCUを採用しなくても利用できる(Intel 3で言えばM7層以上にほぼ等しい)ことを考えると、おそらくeCUはM0~M4までのみに採用されているものと思われる

(※):銅配線の外側にコバルトの薄膜を付けることでエレクトロマイグレーションを抑えるとともに寄生容量や配線抵抗を抑える構造

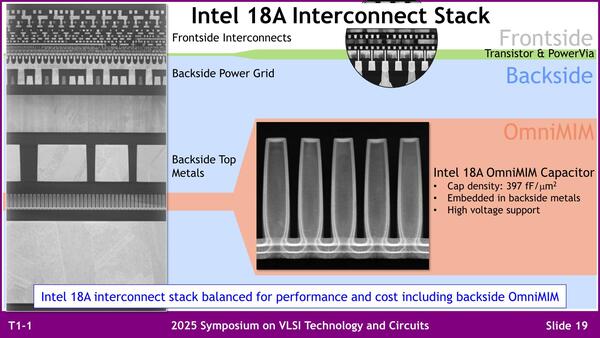

またPowerVIAの方であるが、こちらにはOmniMIM Capacitorと呼ばれる新しい構造のコンデンサーが構築されるようになった。

高さを上げればもう少し容量は増やせるだろうが、製造難易度(≒製造コスト)も上がってしまうので、そのあたりのバーターを取ったのだろうか? 構造的には従来の延長のようだ。なぜOmniMIMという名称を付けたのかは不明だ

以前、10nm SuperFinの世代でSuperMIM Capacitorという埋め込み型コンデンサーを構築していると説明されたが、これがIntel 4では376fF/μm2とほぼ2倍の容量になった。今回はこれをさらに強化して397fF/μm2まで容量を増やした、としている。これは当然電源供給の安定性に直接つながる話である。

ところで先程から出てきたdirect print EUVの話である。もともとインテルはIntel 4の世代でEUVを使い始めているものの、その利用は極めて限定的という話を連載738回で紹介した。まだ当時のEUV Stepperの習熟度では、全面的にEUVを使うのは厳しかったようである。

ただFinFETはがんばればSAQPなどで構築できても、RibbonFETはかなりの部分EUVを使わないときれいなRibbonを構築するのは難しい。そこで、がんばってEUV Stepperの習熟度を上げたのだと思われる。そしてある程度使えるようになったら、トランジスタだけでなく配線層(特にM0~M4の微細な配線層)にも使った方が効果的である。

下の画像がそのdirect print EUVであるが、すべての作業をEUVベースで行なっていることが明らかにされた。もちろんこれはM0~M4までの話で、それ以上の配線層などは別にEUVを使わなくても十分構築できるので、引き続きArF+液浸のままだろうと思われる。

Intel 18Aは、すべての作業をdirect print EUVで行なっている。ということは、Intel 4/3では"Flexible Metal ETE Spacing"と"Bi-Directional Metal Routing"にのみEUV Stepperを使っていたわけだ

このRibbonFETと配線層を組み合わせることで、Intel 18AのSRAMはIntel 3と比べて30%以上密度を上げられた、としている。Intel 18Aの場合、HCC(高速)型で0.0230μmm2/bit、HDC(高密度)で0.0210μmm2/bitとされる。ただこれが十分か? というと微妙なところである。

TSMCのN2ではSRAMの密度が38.1Mbit/mm2という数字を連載810回で説明したが、数字を並べると下表のようになっている(TSMCの方はおそらく高密度型の数字だろう)。

| SRAMの密度 | ||||||

|---|---|---|---|---|---|---|

| 面積(μm2/bit) | 密度(Mbit/mm2) | |||||

| Intel 3 HCC | 0.0300 | 22.260 | ||||

| Intel 3 HDC | 0.0240 | 27.825 | ||||

| Intel 18A HCC | 0.0230 | 29.035 | ||||

| Intel 18A HDC | 0.0210 | 31.800 | ||||

| TSMC N7(HDC?) | 25.0 | |||||

| TSMC N5(HDC?) | 32.2 | |||||

| TNSC N3(HDC?) | 34.1 | |||||

| TSMC N2(HDC?) | 38.1 | |||||

Intel 3はTSMC N7よりはマシだがN5にはおよばず、Intel 18AでもTSMCよりやや低い。理由の1つは配線層だろう。TSMCはまだN2のCPPを公開していないが、N3が45nmであることは2022年に発表済であり、N2がこれより大きいとは思えない。CPPを50nm未満にできないあたりがIntel 18Aがそれほど密度を上げられない要因として挙げられるだろう。

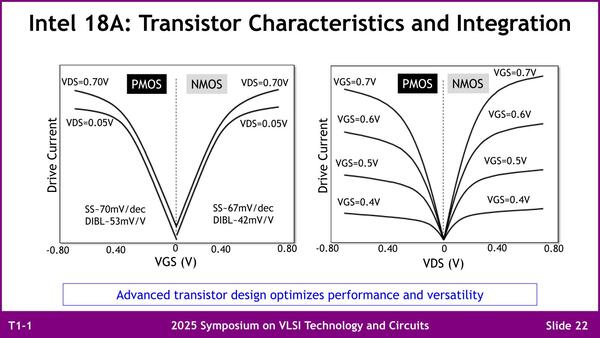

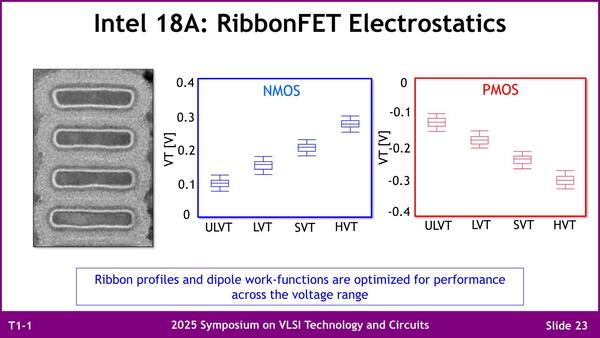

RibbonFETの特性に関して言えば、下の画像がI-V特性であるが、Intel 3の時と比較して、SS(Subthreshold slope)/DIBL(Drain-induced barrier lowering)ともに若干Intel 3より改善されているほか、VGS=0.4Vの時における動作が改善されているように見えるが、肝心の電流値が明示されていないのではっきりと断言はできない。

NMOS/PMOSともに4電圧をサポートしているのはIntel 3に同じだが、電圧そのものはより低くなっており、より効率的に動作するようだ

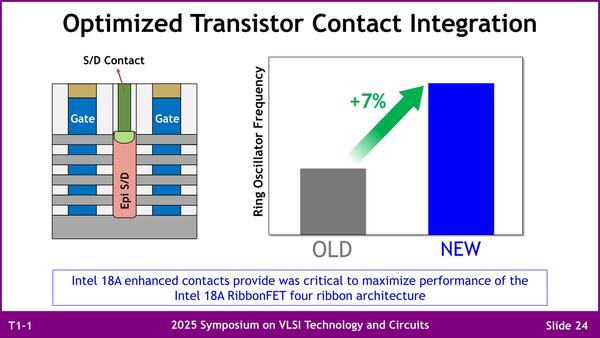

あとSource/Drainの接点部の接続方法を改良した結果、動作周波数が7%向上したという。

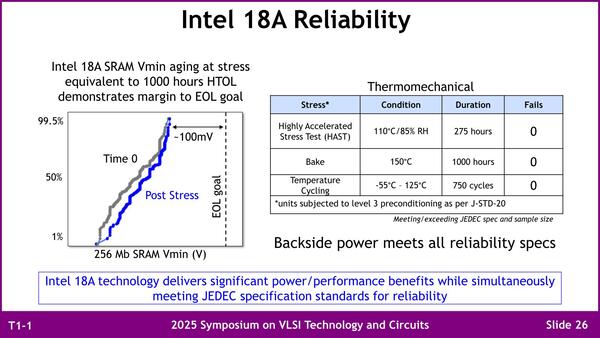

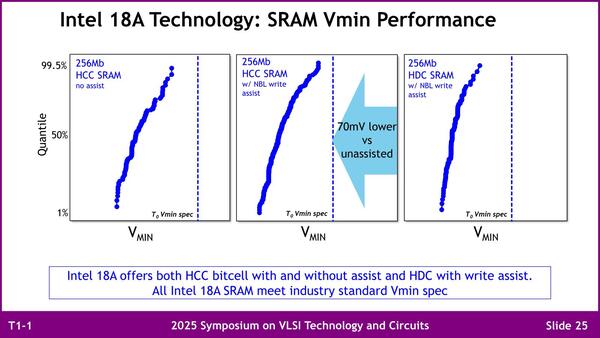

それとSRAMに関してはNBL(Negative Bit Lane) write assistという機構をオプションで用意しており、これを利用すると70mVほど動作電圧を下げることも可能としている。

NBL write assistそのものはIntel 18Aで初めてではなく、すでに広く知られた技術である。HCCで大きくVminを下げられるのはわかったが、HDCの場合はどの程度の効果があるのだろう?

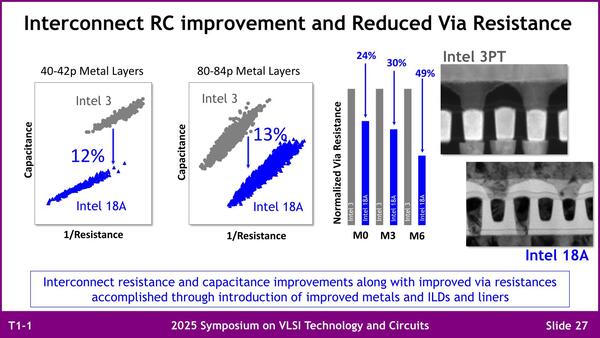

最後に信頼性についてだが、1000時間のHTOL(High Temperature Operating Life:高温動作寿命)テストを終えた後も、EOLとなるゴールにまだ100mVほどのマージンが残されており、十分実用に耐えるとしている。それと配線およびVIAの抵抗が低減されたことにも言及した。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ