最新パーツ性能チェック 第450回

Ryzen 9000シリーズの成長を見守る

AGESA 1.2.0.2でRyzen 9 9950Xのパフォーマンスは改善するか?

2024年09月27日 18時00分更新

Ryzen 9000シリーズの発売以来、様々な検証を行ってきたが、Ryzen 9000シリーズのローンチは順風満帆とは言えるものではなかった。まず初期ロットの品質問題による発売延期、次にTDP 65Wで出荷されたRyzen 7 9700XおよびRyzen 5 9600Xのパフォーマンスが前世代に比して大きく伸びないという批判に端を発してTDP 105Wモードが実装された。

それからRyzen 9000シリーズの発売後にAMD公式発表の性能と市井のレビュアーによる性能が乖離していることが発覚、間もなく分岐予測改善のコードを含むアップデート(KB5041587)がWindows 11に実装された。ちなみに現時点ではKB5041587の単体導入はできないが、Windows 11のビルド22631.4112以降では同じ分岐予測改善のコードが統合されている。

そしてAGESA 1.2.0.2に準拠したBIOSでは、Ryzen 9 9950XおよびRyzen 9 9900Xのコア間レイテンシーが大幅に改善するという報告が上がった。これを検証しないわけにはいかない。

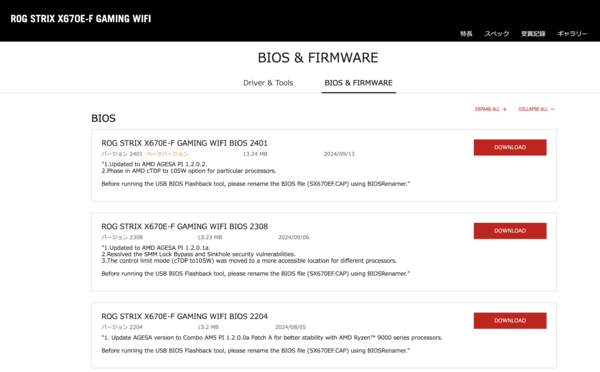

ASUSは同社製Socket AM5マザー向けにAGESA 1.2.0.2に準拠したBIOSの提供を開始した。9月19日時点ではまだβ版扱いなので取扱には注意が必要だが、Ryzen 9 9950Xおよび9900Xのユーザーは試してみる価値があるだろう

そこでRyzen 9000シリーズの成長を見守るシリーズ第3回目は、このAGESA 1.2.0.2導入前・後でRyzen 9 9950Xのパフォーマンスがどの程度改善したかを検証していこう。

Ryzen 9 9950Xと7950Xで検証する

今回の検証環境は以下の通りだ。CPUはRyzen 9 9950Xと7950Xを選択した。両者はどちらも物理16コアCPUであり、内部構造はCCD2基+IOD1基という構成となっている。大きな違いといえばCCDがZen 5世代なのかZen 4世代なのか、あとはPPTが200Wなのか230Wなのか程度だ。

検証用マザーはこれまでの検証記事とは少々変更している。マザーをAGESA 1.2.0.2対応BIOSが提供されたASUS製「ROG STRIX X670E-F GAMING」に変更し、2種類のBIOSで性能を比較した。ひとつはAGESA 1.2.0.1A準拠の2308、もうひとつはAGESA 1.2.0.2準拠の2401である。KB5041587より実装された分岐予測改善のコードを含むWindows Updateはすべて導入済みだ。

また、Secure Boot/ Resizable BAR、メモリー整合性やHDRといった設定は一通り有効化した。GPUドライバーはRadeon Software 24.8.1を使用している。

| テスト環境 | |

|---|---|

| CPU | AMD「Ryzen 9 9950X」 (16コア/32スレッド、最大5.7GHz) AMD「Ryzen 9 7950X」 (16コア/32スレッド、最大5.7GHz) |

| CPUクーラー | NZXT「Kraken Elite 360」(簡易水冷、360mmラジエーター) |

| マザーボード | ASUS「ROG STRIX X670E-F GAMING」(AMD X670E、ATX、BIOS 2308/ 2401) |

| メモリー | Micron「CP2K16G56C46U5」(16GB×2、DDR5-5200/ DDR5-5600) |

| ビデオカード | AMD「Radeon RX 7900 XTX」リファレンスカード |

| ストレージ | Micron「CT2000T700SSD3」(2TB、NVMe M.2 SSD、PCI Express Gen5) |

| 電源ユニット | Super Flower「LEADEX PLATINUM SE 1000W-BK」(1000W、80PLUS Platinum) |

| OS | Microsoft「Windows 11 Pro」(23H2) |

CCDを跨ぐレイテンシーは半減したが……

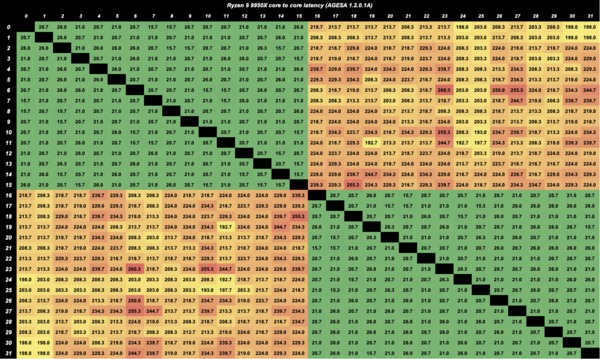

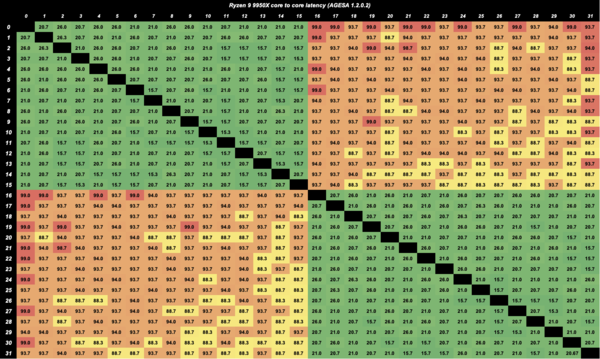

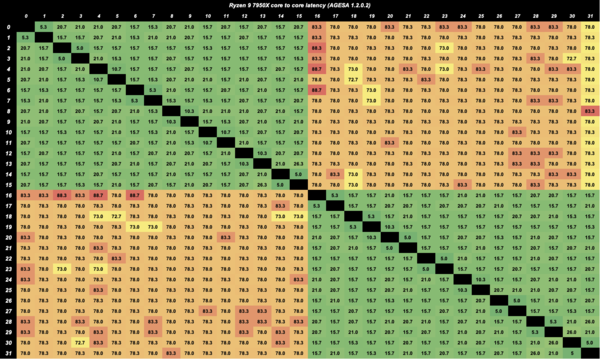

まずはAGESA 1.2.0.2でRyzen 9 9950Xのコア間レイテンシーはどうなったのかを確認しておこう。今回はシンプルで実行も速い「core-to-core-latency」を使用する。すべての論理コアの間で総当たり的に通信を実施し、要した時間(ナノ秒単位)を計測するというものだ。

CCDが複数ある(もしくは1CCD内にCCXが複数ある)AMD製CPUでは、同じCCD(CCX)内のコア同士であればレイテンシーは短いが、異なるCCDやCCXにアクセスする場合はレイテンシーが激増してしまうという特性はRyzen 3000シリーズの段階から知られている。要するに共有L3で結合されたコア同士であればレイテンシーは問題ないが、L3を共有していないコア同士のやりとりが遅いというのがRyzenの弱点である。

テストは各論理コア間の通信を総当たり的に5000回ずつ実施し、レイテンシーの平均値を求め、それをヒートマップ化した。以下のヒートマップでは数値が低いほどいいことになる。また、黒いマスは同じ論理コア同士へのアクセスであることを示す。

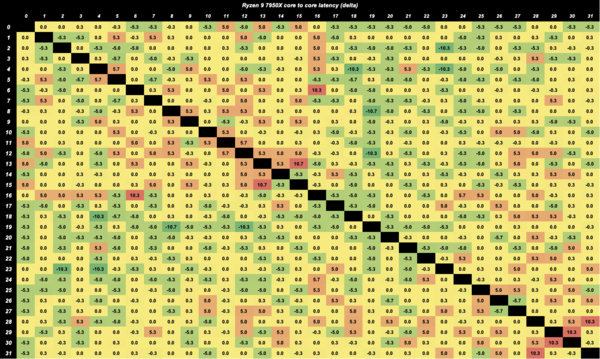

Ryzen 9 9950Xにおけるレイテンシーの短縮効果は非常に大きいことがわかる。AGESA 1.2.0.1AではCCD内であれば20ns台で済むが、CCDを跨ぐような場合は200~240nsと非常に長時間待たされる。ところがAGESA 1.2.0.2ではCCDを跨いだコアへのレイテンシーは90ns台に短縮。一挙に半分以下になったわけだ。

しかし、同一CCD内のコアに対するレイテンシーはまったく変わっていない。差分で見ると同一CCD内でも-10.7ns(わずかながら改善している)や5.3ns(逆に悪化している)部分はあるが、これは誤差の範囲だ。

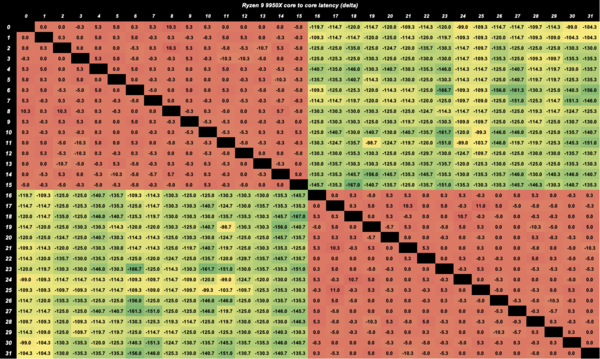

一方、Ryzen 9 7950XではAGESA 1.2.0.2にしてもレイテンシーはほとんど変化していない。差分の分布(3枚目)を見ればわかる通り、CCDを跨ぐ・跨がないに関係なく0±5nsの範囲に収まっているサンプルが大多数で、ところどころ10nsの差が付いた程度。この程度であれば先の例と同様に揺れの範囲内といえる。

AGESA 1.2.0.2はRyzen 9000シリーズのレイテンシー改善にターゲットを絞ったものであり、それ以前のRyzenには効果がないものである、といえるだろう。

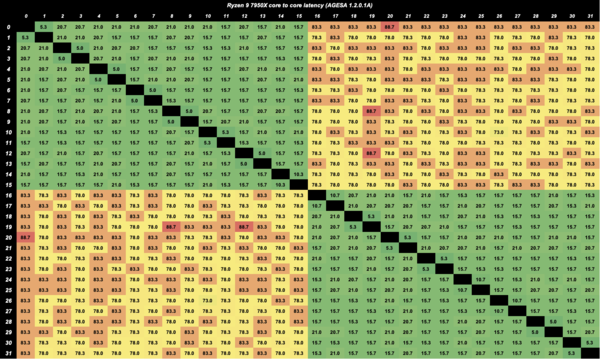

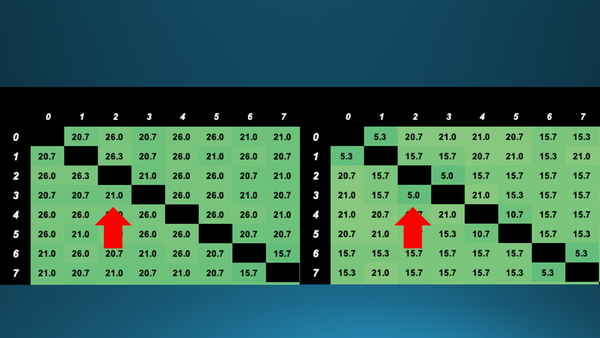

ただこのレイテンシーのヒートマップを眺めているともう一つ気づくことがある。Ryzen 9 9950Xは同CCD内のレイテンシーが若干7950Xのそれより増えているが、特に同一物理コア同士のレイテンシーが増えているのだ(下図参照)。

Ryzen 9 7950Xと9950Xの“CCD内レイテンシー”に注目した図。Ryzen 7 7950X(右)は論理コア1→0や3→2といった“同物理コア内”のレイテンシーが5ns台、長くて10ns台と非常に短いのに対し、Ryzen 9 9950X(左)は20ns以上に遅延している(赤矢印部分)

Ryzen 7000シリーズまでは同ー物理コア内の論理コア同士のレイテンシーは5~10ns程度だが、Ryzen 9 9950XではAGESA 1.2.0.2導入前・後に関係なく20ns以上になっている。Zen 5アーキテクチャーでは命令実行に関わる様々な要素に対し改善が入ったため、少々のレイテンシーは犠牲になったと考えることもできる。

ただその一方で、Zen 1〜Zen 4のSMTが抱えている脆弱性を設計的に乗り越えるためという観測もある。従来のZenファミリーではマイクロコードで緩和できない脆弱性を設計的に解決しようとしたからこうなった、という話である。ただこの観測をポジティブに裏付ける情報は得られていない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第475回

自作PC

Core Ultra 7 270K Plusは定格運用で285K超え!Core Ultra 5 250K Plusは265Kにほど近い性能 -

第474回

自作PC

Core Ultra X9 388H搭載ゲーミングPCの真価はバッテリー駆動時にアリ Ryzen AI 9 HX 370を圧倒した驚異の性能をご覧あれ -

第473回

デジタル

Ryzen 7 9800X3Dと9700Xはどっちが良いの?! WQHDゲーミングに最適なRadeon RX 9060 XT搭載PCの最強CPUはこれだ! -

第473回

自作PC

「Ryzen 7 9850X3D」速攻検証:クロックが400MHz上がった以上の価値を見いだせるか? -

第472回

sponsored

触ってわかった! Radeon RX 9070 XT最新ドライバーでFPSゲームが爆速&高画質に進化、ストレスフリーな快適体験へ -

第472回

自作PC

Core Ultraシリーズ3の最上位Core Ultra X9 388H搭載PCの性能やいかに?内蔵GPUのArc B390はマルチフレーム生成に対応 -

第471回

デジタル

8TBの大容量に爆速性能! Samsung「9100 PRO 8TB」で圧倒的なデータ処理能力を体感 -

第470回

デジタル

HEDTの王者Ryzen Threadripper 9980X/9970X、ついにゲーミング性能も大幅進化 -

第469回

デジタル

ワットパフォーマンスの大幅改善でHEDTの王者が完全体に、Zen 5世代CPU「Ryzen Threadripper 9000」シリーズをレビュー -

第468回

自作PC

こんなゲーミングPCを気楽に買える人生が欲しかった Core Ultra 9 285HX&RTX 5090 LTで約100万円のロマンに浸る -

第467回

デジタル

Radeon RX 9060 XT 16GB、コスパの一点突破でRTX 5060 Tiに勝つ - この連載の一覧へ