Sierra Forestはたったの144コア

Emerald Rapidsに続く製品が、Sierra Forestである。今回発表されたのは以下のとおり。

- Intel 3を利用した最初の製品

- 最大144コア

- すでにA0シリコンは研究室に存在しており、初めて電源を入れた状態からOSが起動するまで18時間未満だった

- サンプル出荷を開始。量産出荷は2024年前半中

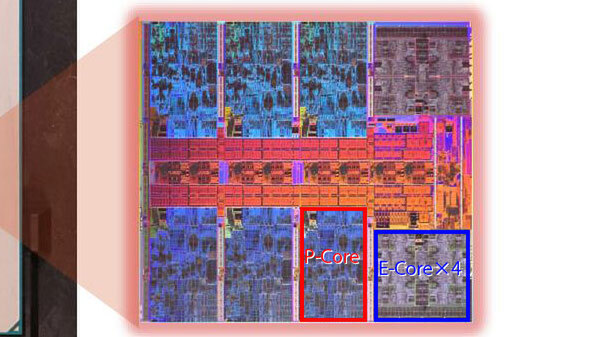

まず意外だったのが、「たったの144コア」ということだ。下の画像は連載675回で紹介したMeteor Lakeのダイ内部の拡大図であるが、Intel 4を使った場合のP-Core×1とE-Core×4の面積比率は1:1.146ほど。

Meteor Lakeのダイ内部の拡大図。元図はこちら(https://ascii.jp/elem/000/003/388/3388167/img.html)

元になるダイをどれにするか悩むが、例えばSapphire RapidsのXCCのコアをベースに考えた場合、Intel 7を使っても最大15コアを収められる面積に52コアほどを収められる計算になる。Sapphire Rapids XCC同様に4タイル構成にすれば208コア分だ。

実際にはSierra Forestはスケールアウト向けなので、1プロセッサーないし2プロセッサー構成であり、となるとUPIはソケットあたり1~2個で済むだろうし、Sapphire RapidsほどにPCI Expressを用意する必要もないから、タイルあたり62~63コア、全体では248~252コアも可能だろう。

Intel 7を使ってもこれだから、Intel 3ならさらにコア数を増やせると考えても不思議ではない。以前の情報では334コアや512コアという話も流れて来ていた。

実際にはメモリー帯域がボトルネックになるだろうから、それなりの3次キャッシュを積まないと、こんなに大量のコアがあっても仕方がない。そう考えるとIntel 3を使っても256コア程度が妥当な数字ではないか? などと皮算用してただけに、この数は少し意外だった。

もちろんこれでもAMDのZen 4cベースのBergamo(128core)よりはコア数が多いものの、実効性能ではどうか? というのは怪しいところだ。

ちなみにBergamoはSMT対応である。Gracemontは、現在はハイパースレッディング無効のままで実装されているが、元になったTremontコアそのものはSMT対応の実装になっているから、Sierra Forestがハイパースレッディングを有効化して出荷される可能性もまだ残されている。

さて、現状はA0シリコンができている状況であるのはわかった。これをAlder Lakeの時のスライドに当てはめると、“T-15m”の“Power On”の状況である。つまりここから出荷まで15ヵ月でこなしたわけだ。

同じスケジュールでいけるとすると、最短で2024年6月になる。辛うじて「量産出荷は2024年前半中」の公約が守れるギリギリというあたりだ。

ただこれ、「Sierra Forestに関しては検証をコンシューマー向けのAlder Lakeと同程度に抑えることで無理やりにでも2024年前半中に出荷する」の意味なのか、「シリコンの状況が非常に素晴らしく、検証でも一切問題が出ない結果として2024年前半中に出荷できる『予定』」なのか。どちらかというと後者の意味合いが強い気が非常にしてならない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ