次世代のBlackholeではRISC-Vを搭載

Tenstorrentの方向性が変わっていく

次はこれに続くBlackholeの話である。連載599回の冒頭でJim Keller氏がTenstorrentに加わった話をしたが、Keller氏はこのBlackholeから本格的に作業に加わったようだ。

2022年に入って、Tenstorrentは猛烈な勢いで人材を集めている。まず2022年2月9日にはArmのMachine Learning Research LabでSenior Director兼Distinguished EngineerだったMatthew Mattina氏をVP of Machine Learningとして引き抜き、6月22日にはLenovo NECの社長だったDavid Bennett氏をChief Customer Officerに据えている。

今年1月23日にはGoogleでStrategic AlliancesのDirector職だったKeith Witek氏をCOOとして迎え入れた。これに先立つ1月20日、同社は創業者兼CEOだったLjubisa Bajic氏とCTOだったJim Keller氏が役割を交代。Bajic氏がCTOとなり、Keller氏がCEOになるという、あまり類を見ないCEO交代劇が演じられている。

実を言えばBajic氏は2003~2013年と2014~2016年にAMDに在籍しており、Keller氏がAMDにいた2012~2015年にはわりと近い位置(2012~2013年はSr. Manager/Architect, IC Design、2014~2016年はDirector, IC Design/Architect)で仕事をしており、ある意味よく知った仲間であったからこそ実現できたことかもしれない。

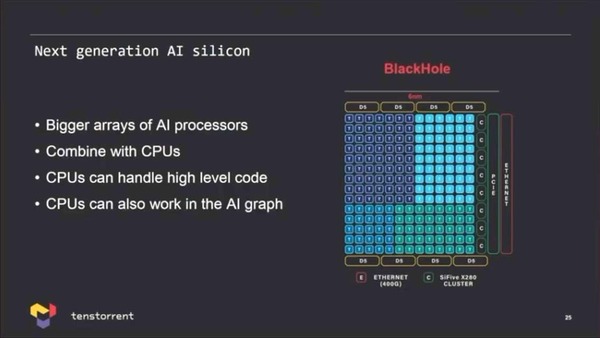

こうした人材の拡充と一緒に、Tenstorrentの方向性もまた少し変わってきた。2022年1月に開催されたTSMCのOpen Innovation Summitにおける基調講演にKeller氏がTenstorrentのCTOとして講演したのだが、次世代の製品であるBlackholeはTSMCのN6で製造され、しかもTensixコアに加えてRISC-Vのコアと、さらにはSiFiveのX280ベクトルコアを搭載することを明らかにしている。

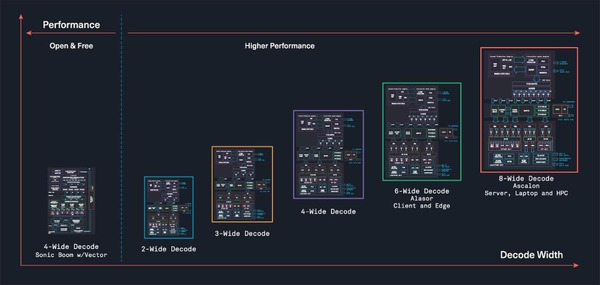

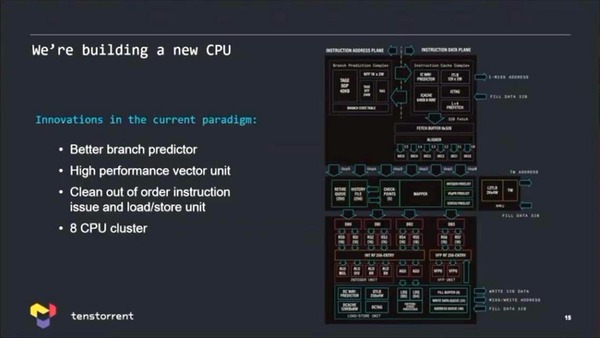

実は昨年からTenstorrentのProductsページにRISC-Vが加わっており、無償で提供されている4命令のアウト・オブ・オーダーコアのOcelotというコア以外に商用で2/3/4/6/8命令デコードのアウト・オブ・オーダーのAscalonというRISC-Vコアを開発しているとしている。D5というのはこのうち6命令デコードのコアの模様だ。

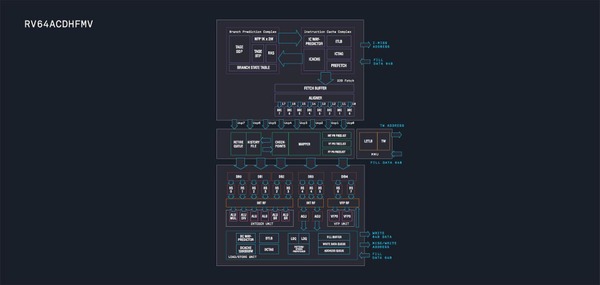

RISC-VコアのAscalon。Vector Unitも搭載しているのだが、X280とどう併用させるつもりなのかは不明

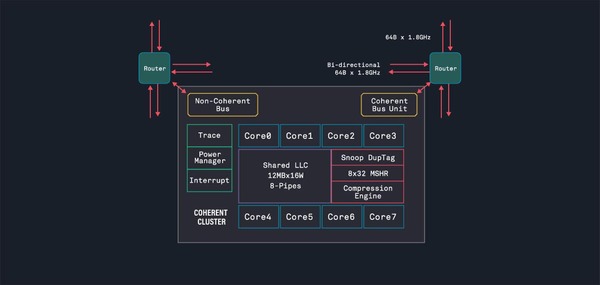

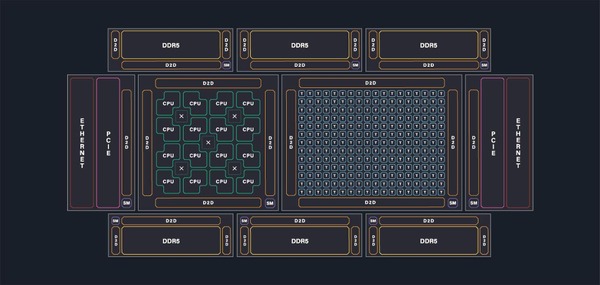

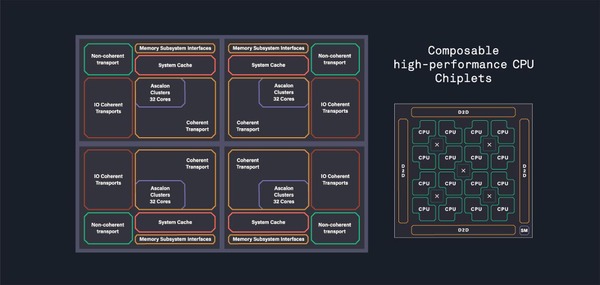

ちなみにTenstorrentはRISC-Vのみでもビジネスする気が出てきたのか、最大8命令同時デコード、11命令同時発行のコアや、そうしたコアを集約するCoherent Clusterを用意し、これとTensixコアを組み合わせた構成やAscalonだけを128コア組み合わせた構成なども示されているが、これはあくまでも可能性を示したレベルであって、これで現実に製品を提供するというつもりはなさそうである。

左側の中の“Ascalon Clusters 32 Cores”の内訳が右側。この右側のものが2つで、1つの32コアクラスターを構成するのだろう。ちなみにAscalonクラスターそのものは1つのシリコンを前提にしているが、こちらはAegis CPUという名称で、チップレットベースになるとの説明がある

ただこれまではTensixコアで高効率にAIワークロードを処理する方向だったのが、Tensix+汎用(RISC-V)コアで、高効率に処理する方向に変わってきており、またKeller氏の基調講演の内容は、複数のネットワークモデルを同時に(Blackholeに)載せて、最適なものを利用するといった方法だったあたり、同社の方向性そのものが以前から少し変わってきた気がする。

サーバー向けのRISC-VコアやチップレットベースCPUなどもラインナップしているあたりは、もう単にAIのスタートアップというよりは、もっと幅広い市場に食い込むことを考えているのかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ