Tensixコアは縦横4方向のリンクを持つ

しかもNOCはマルチチップ構成で非常に有用

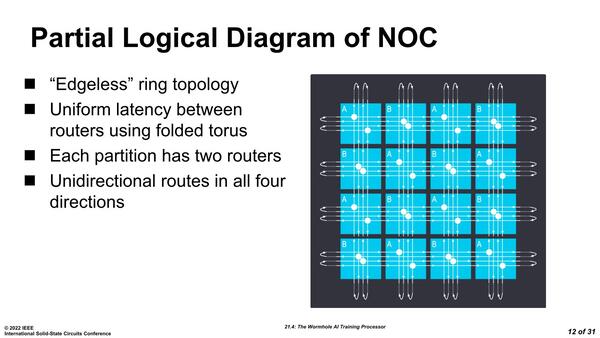

さて、GrayskullでもTensixコア同士はNoCで接続されているという話があったが、これはWormholeも同じである。下の画像がWormholeのネットワーク構成だが、すべてのTensixコアには2つのルーターが置かれ、それぞれのルーターは縦方向と横方向の2対のリンクを保持しており、結果としてTensixコアは縦横4方向のリンクを持つ構造になる。

このメッシュの上でNOCを構築するのはGrayskullと同じである。ただGrayskullではこれをNOCにする意味が今ひとつ不明だったのだが、続くスライドでその意味が完全に理解できた。

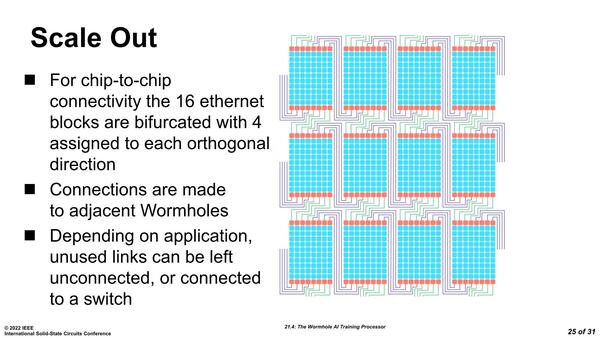

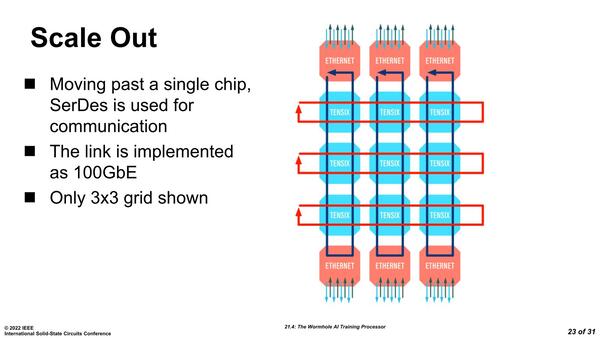

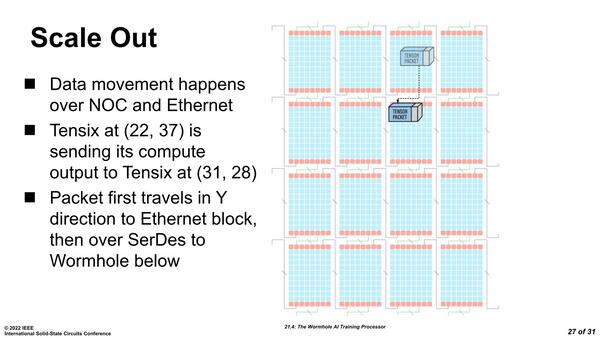

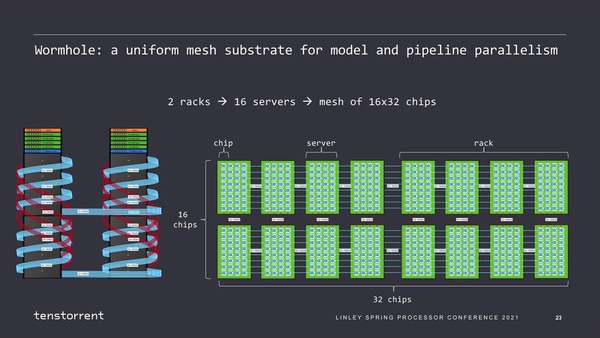

先にも書いたように、Wormholeは100GbEを16本搭載し、これを利用してチップ間接続が可能になっている。上の画像はこのWormholeを12個集約した例であるが、16本のGbEを4本づつに分けたうえで、それぞれ上下左右のWormholeと接続する格好である。

この際にリンクはGbEを経由して外部に引っ張り出される形になる。

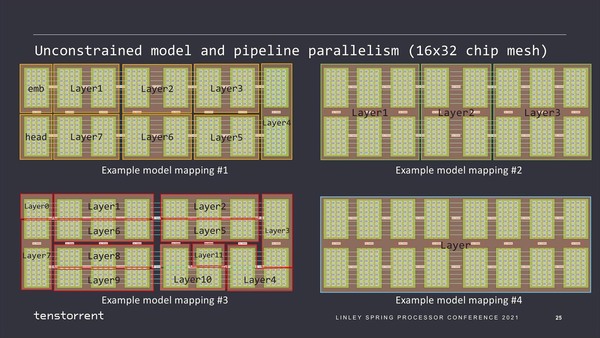

この構成で言えば、80×12=960個のTensixコアが特にパーティションもなにもない、均一な形で接続されているようにプログラマーからは見える。こうなってくると、NOCを利用するメリットは明確である。

Wormholeが1チップで動作しているのであれば、NOCのメリットはあまり感じられないが、物理的にどうつながっているかケースバイケースのマルチチップ構成でプログラミングをすることを考えると、NOCは非常に有用である。

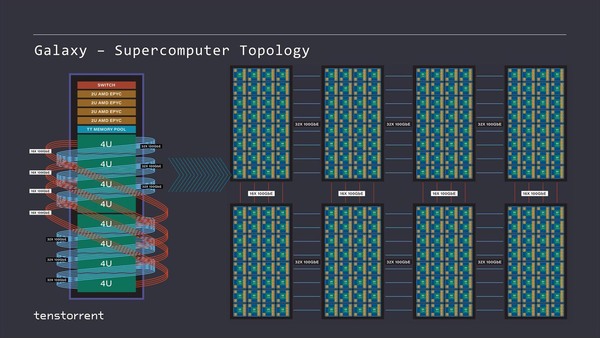

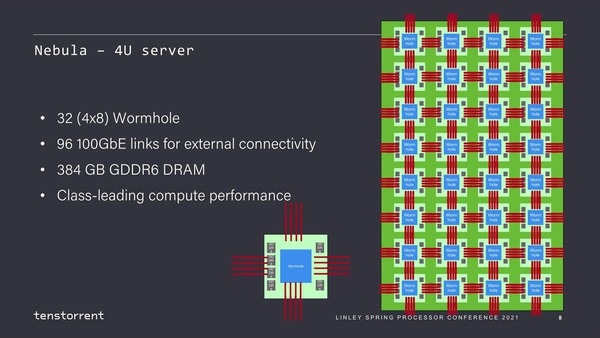

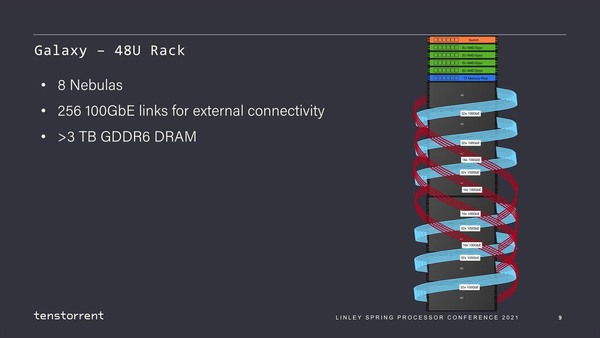

ちなみに2021年の計画では、このWormholeを32個つないだNebulaが4Uサーバーとして提供され、このNebulaを8つ搭載した48UのラックがGalaxyとされていた。

4Uというあたり、基板は2枚でそれぞれに16個のWormholeが載る構成(あるいは8個のWormholeを乗せた基板が4枚か、もしくは4個のWormholeを乗せたドーターカード8枚がキャリアボードにささる格好だろうか?)を考えていたように思われる

管理用に2UのEPYCサーバー×4と、メモリープール、それとToR(Top Of Rack)スイッチが載っているのがわかる。メモリープールが今ひとつ正体不明である。CXLベースのメモリーアプライアンスとも思えないのだが……

そのGalaxyの内部結線を分解したのが下の画像だ。

このGalaxyでは256個のWormholeが搭載され、Tensixコアはトータル2万480個、演算性能はFP16で110PFに達する。そして必要なら複数ラックをつないでさらに大規模な構成を構築することも可能だ。

そして内部は、レイヤーの複雑さに応じてTensixコアの塊を任意のパーティションに区切ってそれぞれ処理させることで効率を上げられるとする。

1つのTensixで複数レイヤーの処理をさせるのはオーバーヘッドが大きすぎるのでこれは合理的ではあるのだが、逆に言えば小規模なWormholeの構成では不効率さが目立つことになる。Nebulaでもまだ不十分で、Galaxyクラスでやっと効率的に処理できるようになる、というあたりだろう

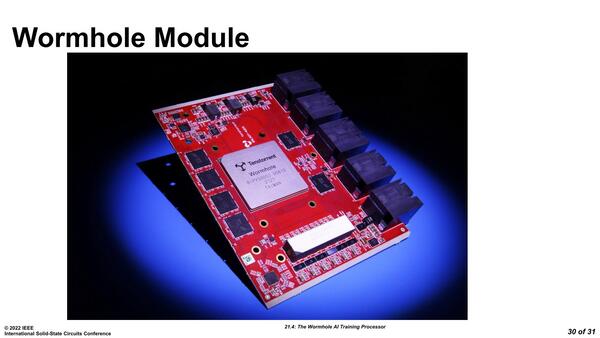

昨年2月の時点ですでに最初のサンプルはできあがっていたようで、予定では2022年第4四半期に出荷という話であったが、今のところまだ発表がないあたりはやや遅れているようだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ