ロードマップでわかる!当世プロセッサー事情 第578回

Ice Lake-SPはスループットがSkylake-SPの2倍以上になる インテル CPUロードマップ

2020年08月31日 12時00分更新

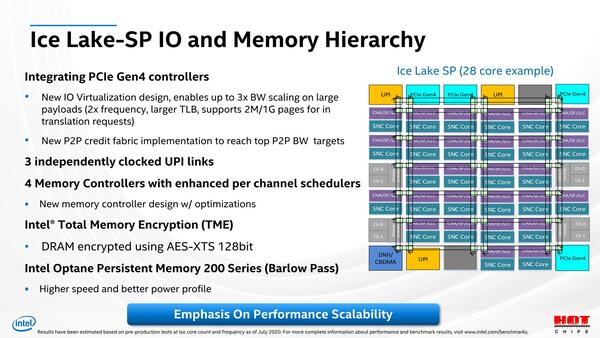

DDR4-3200とPCIe Gen4に対応

CPU内部を分割すると妙に対称性に欠ける

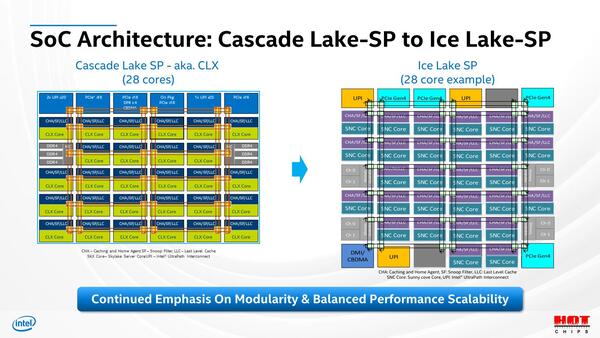

さて、次はコア全体の話だ。Cascade Lake-SPとIce Lake-SPの内部構造を比較したのが下の画像である。

Cascade Lake-SPとIce Lake-SPの内部構造を比較したもの。Cascade Lake-SPは全体が6×6で36ブロック、Ice Lake-SPはこれが6×7で42ブロックとなり、うち2ブロックが未使用となっている

- メモリーコントローラーブロックが4つ(Cascade Lake-SPは2つ)に増え、各々2chのメモリーをサポート(Cascade Lake-SPは3つ)

- UPIが3つ(Cascade Lake-SPは2つ)に増強

- PCIeのブロックそのものは4つで共通だが、Cascade Lake-SPはうち1つがDMI/CBDMAと共通だったのに対し、Ice Lake-SPではこれが別に設けられることなったので、実質PCIe x16レーンが1つ余分に利用できるようになった

一見すると違いは上記のあたりだろうか。メモリーコントローラーがDDR4-3200に対応したほか、各メモリーチャンネルあたり1枚のNVDIMMを利用できるようになった。またPCI ExpressはGen4に初対応したといったところになる。

ちなみにこれは「28コアの例」であって、Cascade Lake-SP世代ではこれはHCC(High Core Count)の扱いだったが、どうもIce Lake-SPではこれはMCC(Middle Core Count)の扱いの模様だ。ただそうした詳細な製品SKUは今回明らかにされていない。

このコアの配置で気になるのは、CPU内部をパーティショニングしたい場合だ。従来Skylake-SPやCascade Lake-SPでは、内部を複数の別々のCPUに分割して使うことが可能だった。

上の画像の例で言えば、中央で二等分することで、14コアとメモリーを3ch、PCIeを2つとUPI×1を持つCPUが2組に分割できることになる。ところが同じことをIce Lake-SPでやると、13コアと15コアという、妙に切りの悪い分割になる。

PCIeおよびメモリーに関しては、どちらも2ブロックづつになるが、UPIは片方が2組、もう片方が1組になるという、妙に対称性に欠ける構成になるのはどうしたものか。MCCグレードのCPUは分割して使わない、という話なのかもしれないが。

また別のスライドによれば、Cascade Lake-SPではI/O Agentがコアの上側に集中しているが、Ice Lake-SPではこれを上辺と下辺に分割したと説明があり、ひょっとすると左右ではなく上下に分割するのかもしれない(その場合、16コアと12コアという、さらにバランスの悪い構成になる)。

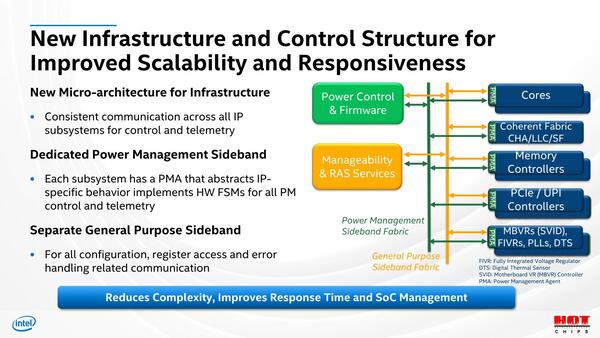

そのインターコネクトであるが、新たに汎用と電力管理用のSideband(メインとは別に設けたバス)が追加されたとしている。

汎用と電力管理用のSidebandが追加。AMDで言うなら、このPower ControlやManageability&RAS ServicesというのはInfinity FabricのControl Fabricに相当する。データそのもののやり取りをするData Fabricと分離する形で進化するのは、ある意味必然なのかもしれない

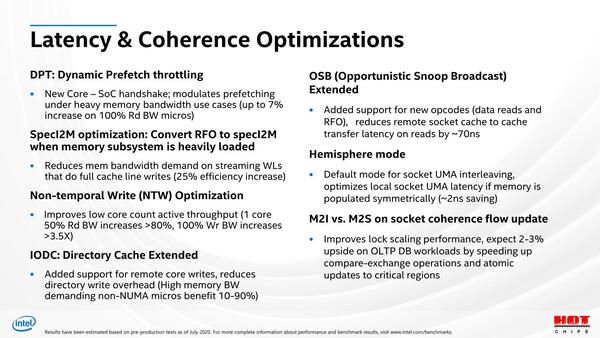

またインターコネクトとメモリーコントローラーにも関係する改良点が下の画像だ。

RFO(Read for ownership)をSpecI2M(Invalid to Modified)に置き換えてキャッシュを制御する、Non Temporal Writeへの最適化を行なうなど、細かな項目が並んでいる。

ちなみにメモリーコントローラーは、新しくDRAMの内容をAES128で自動的に暗号化する機能が付加されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ