さて、今週からHot Chips 32で公開された情報をいろいろ解説していきたい。まずはTiger Lakeからだ。といっても実はTiger Lakeに関しては先々週開催されたArchitecture Day で公開されたものとあまり大きな差はなかった。

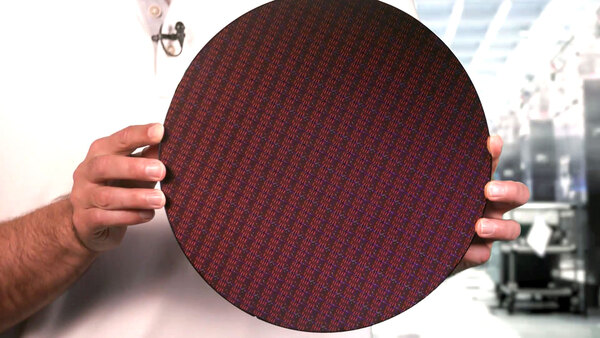

Architecture DayでTiger Lakeのウェハーを示すBoyd Phelp氏(VP Client Engineering Group, GM Client and Core Development Group)

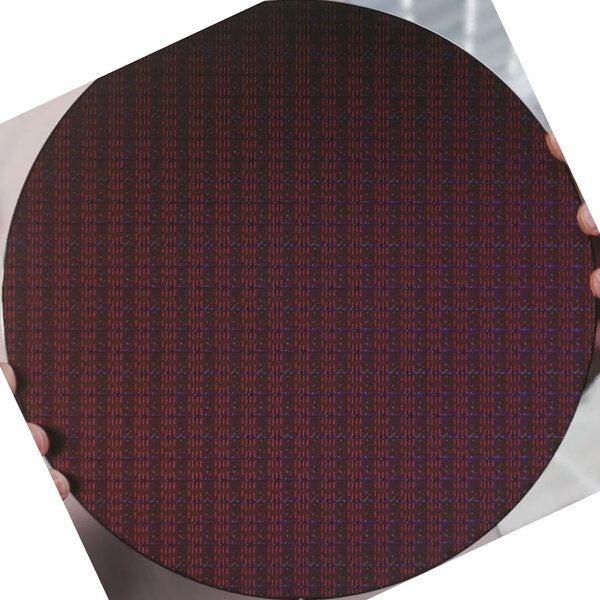

まずこのウェハーから。上の画像の角度および縦横比をできる限り補正したのが下の画像だ。

ラフに言ってこの写真で300mmウェハーは「縦方向:27.5ダイ分、横方向22.5ダイ分」という感じで、ここからダイサイズはおおむね10.9×13.3mmでほぼ145mm2程度と推察される。

連載514回でIce Lakeのダイサイズを推定した時は131mm2と見積もったが、実際には122.5mm2らしい。

なので、実際には140mm2を切る程度かもしれないが、いずれにしても20mm2弱、Ice Lakeから大型化したとみられる。寸法からもわかるように、形状は正方形に近い形である。

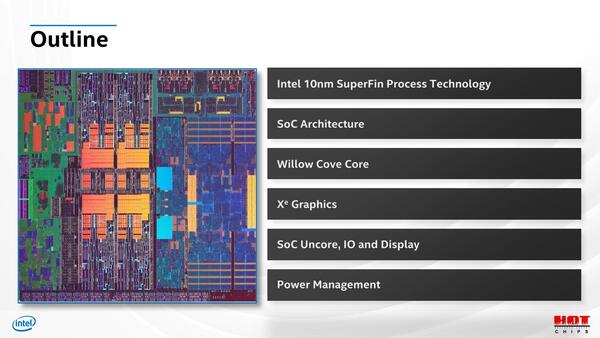

下の画像はHotChipsで公開されたものだが、前述のウェハーに当てはめると縦横比が合わないあたり、少し横方向に圧縮されているように思う。

さてそのTiger Lakeであるが、特徴は以下のとおり。

- 10nm SuperFin Processを採用

- Willow Coveコアを搭載

- Xe-LE GPUを搭載

10nm SuperFin Processについては前回説明しており、Hot Chipsでも特に新情報はなかった。

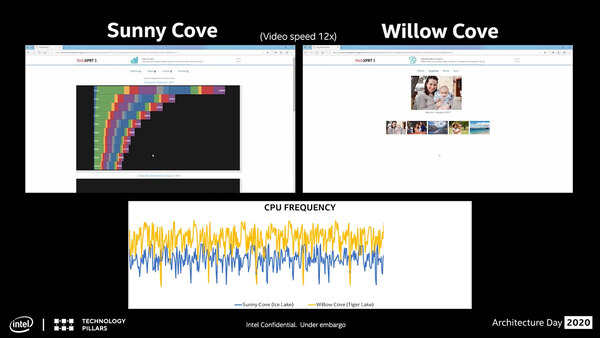

ただ前回も推定したように、定格(25W?)だと1.9GHz、Ice LakeのPL2相当(50W?)だと4.7GHzまで動作周波数が引きあがる。

実際にはPL2がもう少し(65W程度?)まで引き上げられ、この際の動作周波数は5GHzに達するのではないかと思われる。実際Architecture Dayでは同じ処理をIce LakeとTiger Lakeで行なった際に、Tiger Lakeが明らかに高い動作周波数で動作していることが示された。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ