ひさびさにAIプロセッサーの話に戻る。2019年のHotChips 31で、おそらく一番会場を沸かせたのはCerebras SystemsのWSEかと思われる。

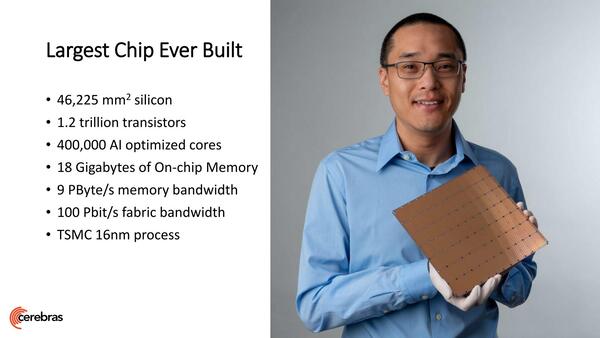

WSEは、TSMCの16FF+で製造された300mmウェハーをまるまる使ったお化けチップである。実はこのチップの話、昨年の8月にもニュースになっているのだが、こちらはあまりにも簡単に済ませているのでもう少しきちんと説明したい。

ダイサイズ4万6255平方mmや1.2兆トランジスタ、40万コアなど、いろいろ数字がインフレし過ぎている気もする。チップ単体でPB/秒という帯域は初めて見た気がする(ちなみに連載570回で紹介した富岳の、システム全体でのメモリーバンド幅が163PB/秒である)

画像の出典は、HotChips 31の“Wafer-Scale Deep Learning”

旧SeaMicroのメンバーが集結し

AI向けプロセッサーを開発

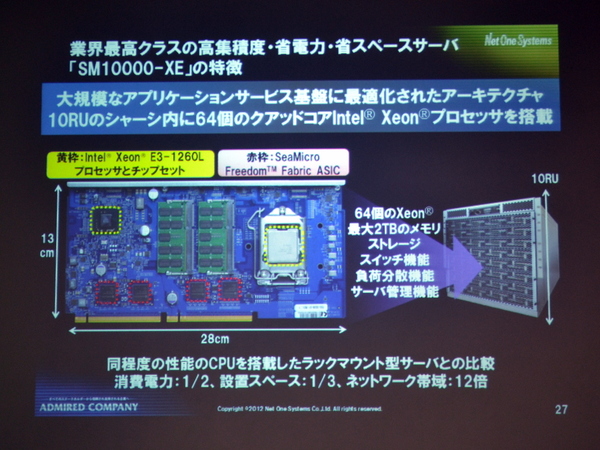

Cerebres Systemsは2016年の創業であるが、創業メンバーのかなりの部分は、旧SeaMicroのメンバーだった。SeaMicroは、SM10000-XEのように小さなコアを多数つなげて高機能サーバーを作ることを得意とする会社で、Freedom Fabricと呼ばれる独自インターコネクトを特徴としていた。

ただSeaMicroは2012年にAMDに買収され、AMDのArmベースサーバーの中核になる予定だった。これが消えたのは結局AMDがOpteron A1100シリーズを発売したのみで後継製品をホールド、Zenコアベースに傾注する方向に行ってしまったからで、それもあってかSeaMicro組は2014~2015年くらいに相次いでAMDを辞職して、再び集まって「なにかやろうぜ」と画策していたらしい。

このメンバーの中核はCerebres Systemsの現CTOであるGary Lauterbach氏であるが、氏はSeaMicroの前に(一度AMD Fellowにもなっているのだが、さらにその前に)Sun Microsystemsに勤めており、この時DARPA(米国防高等研究計画局)のHPCS(High Productivity Computing Systems:高生産性コンピューティングシステム)というプロジェクトに関わっていた。

これは2002~2010年にかけてスーパーコンピューターを構築するというもので、最終的にはIBMとCrayの案がこのプロジェクトでは採択されたが、Sun Microsystemsの案も第2段階までは通っていた。

Sunの案では、チップ同士を少しだけ重なるように配置し、その重なっている部分で無線を利用してチップ間通信を行なう(これはProximity CommunicationとしてSunで研究が行なわれていた)というものである。

このプロジェクト、最終的にはPFlops級のマシンを構築する予定であったが、そうなると当然多数のチップをわずかに重ね合わせながら集積することになる。

Sunのシステムは、300mmのウェハーの上に2500個ものチップを重ね合わせながら積層するという、これはこれでお化けであり、まぁ最終的に第2段階の提案で却下されたので実機は存在しないのだが、この時の経験が少なからずWSEに影響をおよぼしたらしい。

さてAMDを辞したLauterbach氏やLie氏、Michael James氏(Chief Architect of Advanced Technologies)、Jean-Philippe Fricker氏(Chief System Architect)、それとAndrew Feldman氏(CEO)の4人は再び集まり、自分たちの技術でなにができるかを考えたところ、AI向けプロセッサーが有望そうだという結論に達したらしい。

そこから改めていろいろとアイディアを煮詰め、ベンチャーキャピタルに声をかけつつ、かつてのメンバーを呼び寄せるなどしてチームを立ち上げていき、2019年に実際の製品ができあがったというわけだ。

Cerebres SystemsのLeadership teamページで、“Co-Founder”とあるのが上の4人であるが、残りのメンバーも少なからずSeaMicro出身だったりするわけで、そういう意味では再び昔のチームで、という感じなのかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ