非ノイマン型プロセッサーへの挑戦と挫折

新しいプロセッサーの用途が見え始めると、必ず湧いて出るいくつかのアーキテクチャーがある。例えば超ワイドなVLIW(Very Long Instruction Word:超長命令語)や、超ヘテロジニアス・プロセッサー、メモリー・セル・プロセッサー(マトリックス・プロセッサー)などの類だ。

VLIWは確かに実装が楽だからといって、10を超える命令を同時にサポートするのはやはりやり過ぎだと思うし、1つのSoCの中に異なる命令セットを持つコアを複数種類(それも2つとかならともかく4つも5つも)実装し、それらの命令セットをつなげてVLIW化するのは無茶を通り超えて無謀の域に達する。

メモリー・セル・プロセッサーというのは、消費電力を考える演算そのものよりメモリーと演算器の間のデータ移動の方が消費電力が大きいので、メモリー・セルと演算器を一体化したというアイディアである。

これはみんなが思いつくにも関わらず、まともなプロセッサーが存在しないというのは、やはりそれなりに難しさが存在するからで、これにチャレンジして散っていったベンチャー企業は筆者が知っているだけで3つある。

同じように湧いて出るアイディアにデータフロー・プロセッサーがある。日本語ではデータ駆動型コンピューターとするのが一般的かと思うが、実は日本だと1987年に電総研で開発されたSigma-1や1990年のEM-4などを始め、いくつか完成したマシンが存在する。

ただこれは巨大なシステムであって、とてもワンチップに収まるものではない。それでも2000年台に入ると、例えばARMをクロックレスで動作させた疑似データフロータイプのプロセッサーなど、いくつかチャレンジした例はあるのだが、やはり商用的に成功した例はない。

昨今で言うとデンソー子会社のNSI-TEXEが今年1月にDR1000Cと呼ばれるデータフロー・プロセッサーを発表したが、まだ商業的に成功したか否かを判断できる段階ではないのでここではおいておくとして、基本的にデータフロー・プロセッサーは茨の道である。

しかし「非ノイマン型プロセッサー」という言葉にはなにかしらの魅力があるようで、これにチャレンジする企業は後を絶たない。

データフロー・プロセッサーの代表作

Wave ComputingのDFP

ということで本題。2017年のHot Chips 29において、アメリカのWave Computingというベンチャー企業がAI向けにDFP(Data Flow Processor)を発表した。同社はTailwood Capitalの支援を受け、2010年に創業後はステルスモードで活動しており、このHot Chipsにおける発表が会社と製品の初公開の場となった。

さてそのDFP。例えばCPUとGPUを組み合わせて機械学習をやる場合、しばしばGPUがCPUを待つことが多く、非効率であるというのがそもそもの動機である。

この非効率には以下の2つが挙げられる。

- 処理をCPUとGPUで分散させており、なのでGPU側に待ちが発生する

- 待ち時間の間にも電力消費がある

ではすべての処理をGPUでできるように変更すれば解決するかというと、そういう問題でもなく、GPUの負荷が掛かっている時でも、常にすべてのユニットが動いているわけではない。

加えて言えば、GPUは細かな制御を行なうのに向いてない(それを入れたらGPUの良さがスポイルされる)し、全部GPUにしても待機する処理ユニットが電力を消費する問題の解決にはならない。これを解決するのにデータフロー方式が役に立つ、というのが同社の主張だ。

データフローというのは「データが来たら処理を行ない、終わったらそれを次のユニットに送り出して終了」というもので、通常のCPUの「クロック信号に同期して内部の処理ユニットを順次動かす、いわばクロック同期式」とまったく異なる制御方式で動作する。

現実問題としては、個々のユニットの中は従来の同期式のメカニズムで実装される場合もある(ここを完全クロックレスにすると、難易度が急増する)が、上位レベルではクロックとは非同期で、あくまでデータの到来に合わせて非同期で動作する。

これをディープラーニングに応用すると、DFPの演算ユニットに個々のニューロンを割り当てることで、「データが来た時だけ動く」という、もともとの人間の神経細胞に近い動きをナチュラルに実現できる。

加えて言えば、例えば従来の方式では処理結果が0の場合でも、次のユニットにその0が伝搬されるが、データフローの場合は、あるユニットの計算結果が0だと、次のユニットがそもそも動かないから無駄に消費電力を費やすこともない。この結果として極めて効率的に動作できるという主張だ。

どうやってこれでBack Propagation(逆伝搬:学習データからパラメーターを調整する作業)を実施するのかがいまいち明確ではないのだが、それはともかくとしてこのデータフロータイプのプロセッサーとして作り上げられたのが同社のDFPである。

特徴は以下のとおり。

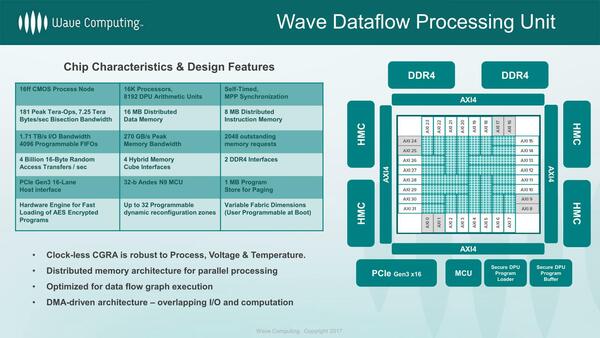

- 非同期動作するプロセッサー1万6384個とDPU算術ユニット8192個を集積。処理性能はピークで181Tops。

- データメモリー16MBと命令メモリー8MBをコア内部に集積。このコア内部のメモリー帯域は7.25TB/秒に達する。

- I/O帯域は1.71TB/秒で、I/O用に4096個のFIFOが用意される。外部メモリーには4つのHMCと、オプションで2chのDDR4が用意され、トータルで270GB/秒の帯域が確保される。

- ホストとのI/FはPCIe Gen3 x16。また内部の管理用にAndesのAndesCore N9 MCUが搭載される。

ここでHBM/HBM2ではなく、Intel/Micron連合の開発したHMC(Hybrid Memory Cube)を選んだのは少しばかり痛恨のミスだったような気もしなくはないが、AMDがHBMを初採用したのは2015年のことで、確か当時AMDはSK HynixとUMC、それとASEの共同開発(チップをSK Hynix、インターポーザーをUMC、パッケージがASE)でやっと実現したという代物で、ステルスモードのベンチャー企業が実現するのは難しかっただろう。

その後TSMCがCoWoSでHBMを普通に扱えるようになったのは、2016年に入って投入された第2世代のCoWoS-XLからで、やはりベンチャー企業には間に合わなかったと考えられる。また、1:1接続ではないのも理由に挙げられよう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ