今週はHPの歴史はお休みいただいて、インテルのプロセス周りの話をいくつか解説したい。といっても、どちらかといえば小ネタではある。

回路が破損する問題を解消した

F-1ステッピングのApollo Lake

今年9月3日、インテルはPCN(Product Change Notification)をリリースし、Apollo LakeベースとなるCeleron N3350/J3355/J3455およびPentium N4200に対してステッピング変更が行なわれたことを明らかにした。

実はなぜかPCNが出ていないのだが、変更後の仕様を見ると、ほかにAtom x5 A3930/3840、Atom x7 A3950/A3960やAtom x5 E3930/3940/3950/3960などにもステッピング変更が行なわれた(F-1 Stepping)ことが明らかになっている(というより、むしろ本命はこちらな気もするのだが、なぜPCNが出ていないのだろうか?)。

さてこのPCN、対象はIOTG(IoT Group)向けとなっている。要するに組み込み用途であり、PCやタブレットなどコンシューマー向け用途には引き続き従来のB-1ステッピングが利用可能と説明されている。

これはなにかという話だが、もともとこの問題は2017年2月ごろに露呈したものである。発端は、インテルのC2000プロセッサーを組み込んだCiscoの製品が一定期間利用(おおむね18ヵ月ほど)後に次々と動かなくなるというもので、2016年11月にこの問題を通知。これが一般に知られるようになったのがその3ヵ月後だったというわけだ。

Ciscoはこれを受けて当然製品の交換その他の対策をとっている一方で、タイトルにこそ“Clock Signal Component Issue”と記しているものの、具体的な問題の内容は記載されていない。

ではどんな問題だったのか? 基本的には、3.3Vを利用するRTC(Real Time Clock)、USB 2.0、LPC Clock、SDカードなどの回路を長期間連続して利用させた場合、その回路が破損することだったそうだ。

こうした(相対的に)高電圧を駆動させていると、そのトランジスタが急速に劣化し、18ヵ月程度で駆動できなくなる(orショートする)ということらしい。

根っこが深いのは、これらの周辺回路はSandy Bridge世代のチップセット(つまり65nmプロセスで製造されたCougar PointことIntel 6シリーズチップセット)で使われた回路をそのまま流用したものらしいことだ。

65nmではトランジスタの絶縁性能が十分高かったのでこれらの問題は露呈しなかったが、14nmまで微細化したことでトランジスタの耐圧が足りなくなった、というあたりだろうか?

もともとIntel 6シリーズは発売当時にSATAポートが劣化するという問題があって、一度リコール騒ぎになっているのだが、SATAだけではなかったという話なのかもしれない。

さて、この問題を受けてインテルは修正を始めるのだが、予想以上に困難だったようだ。インテルは一度、2018年第2四半期に投入されるF-0ステッピングでこれを修正するという予定を立てるが、このF-0ステッピングではテスト中に問題が発生したそうで、ここからもう一度作り直しをしてF-1ステッピングを完成させ、この度リリースされた形になる。

ちなみにAtom E3900/A3900については、このF-1ステッピングの情報が含まれたデータシートの日付が2019年7月になっており、ところが先にも書いた通りPCNデータベースにはこれが記載されていないあたり、おそらくはこっそりとリリースされたのであろう。

さて、どう修正されたのだろうか? Atom 3900シリーズの場合、パッケージはヒートシンクに覆われているのでさっぱり不明なのだが、Celeron N3350/J3355/J3455とCeleron N3350/J3355/J3455およびPentium N4200に関して言えば、PCNでは“slight increase in Z height compared to the B-1 Stepping“(B-1ステッピングと比較して、わずかに厚みが増している)と記されている。

実際には厚みが66μmほど増して、1.384mm±0.1mmになっているので、確かに「わずかに」厚みが増しているわけだが、さてこれはなんであろうか?

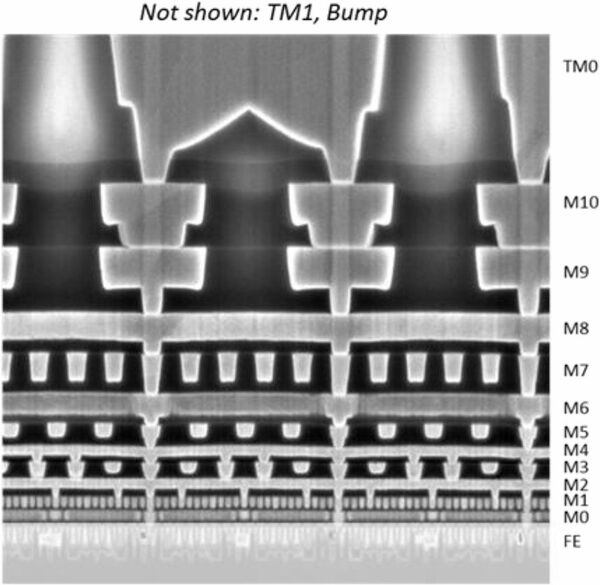

配線層の断面写真は連載464回で紹介した通りである。下の画像は、その10nmプロセスの断面図なので14nmとはやや違うが、10μmオーダーの厚みを持つのはTM0などその上(の写真には載ってない)TM1といった、電源配線層になると考えられる。

画像の出典は、IEDM 2017におけるIntelの“A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects”という論文。

おそらくはTM1の上にTM2とTM3が追加されていると思われ、しかもその下のM1~M9といった信号配線層に関しても層が追加されている可能性がある。

なぜこうなったかといえば、電源の回り込みを根絶するためだろう。従来はTM0/TM1に1.8V/3.3VといったI/O向け電源と、ロジック向けの1V前後の電源の両方の配線層が混在しているが、これが理由で3.3Vの電流がロジック側に回りこみ、トランジスタを劣化させることを防止したのであろう。というより、他の理由が考えられないというほうが正確だ。

また、I/O周りに関してはトランジスタの耐電圧を上げる必要がある。もともとインテルはこうした用途には高耐圧トランジスタをラインナップしているはずだが、これでも耐えられなかったという話である。

耐圧を上げるのにどうすればいいかといえば、駆動するトランジスタを直列にすれば良い。ただFinFETプロセスの場合、並列は簡単なのだが直列となると共通のフィンで横に並べるわけにはいかず、やや配線(レイアウト)のやり直しが必要になる。

このあたりのために、M0あたりに相当する配線層を追加したのではないかと筆者は疑っている。

なんというかこの問題、予想以上にインテルのプロセスはHigh Speed Logicに全振りしていたのだな、というのが率直な感想である。この反省をもとに7nm世代では問題が根絶されていると良いのだが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ