今回は前回に続き、インテルのデスクトップ向けCPUのロードマップについて解説する。前回は現在主流のCore 2シリーズについてまとめたが、今回はこれからの主役である「Core i」シリーズを取り上げよう。

Core iシリーズの特徴をおさらい

Core iシリーズは登場前、「Nehalem」というコード名で知られていたCPUである。非常に特徴の多いCPUなので、順に挙げてみよう。

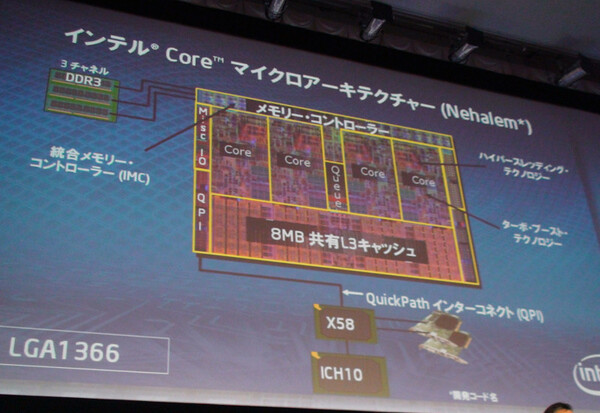

- ネイティブ・クアッドコア

- Core 2 QuadやPentium Dのように、2つのCPUダイをMCM(Multi Chip Module)の形でひとつのパッケージにまとめるのではなく、4つのコアが1つのダイ上に集約された構造。

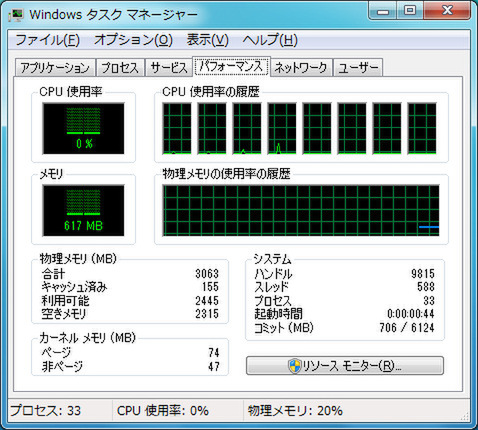

- ハイパースレッディングの復活

- 各CPUコアごとに、2つのスレッドを同時実行できる仕組み。この結果、OSから見るとCPUコアの数が倍増して見える。実際Core i7搭載マシンでWindowsのタスクマネージャーを表示すると、CPUが8つ出現する。

- 共有3次キャッシュを搭載

-

Core 2では、各CPUコアごとに32KBの1次キャッシュ(命令/データ分離)を搭載し、2次キャッシュは各コア共有のユニファイド(命令/データ共通)キャッシュ方式の構造だった。

対してCore i7では、コアごとに32KBの1次キャッシュと256KBの2次ユニファイドキャッシュを搭載。さらに全コア共通の8MBの3次ユニファイドキャッシュという構造になった。 - DDR3メモリーコントローラーを内蔵

- Core 2シリーズまでは、メモリーコントローラーはチップセット側に内蔵され、チップセットとCPUの間をフロントサイドバス(FSB)で繋いでいた。対するCore i7では、CPU側に3チャンネル分のDDR3メモリーコントローラーが内蔵された。

- QPIの採用

- Core i7ではFSBが廃止され、代わりにCPU同士、あるいはCPUとチップセットの接続用に、新しい「QPI」(QuickPath Interconnect)と呼ばれる高速パラレルバスを採用した。

- CPUパイプラインは小変更

-

機能的には、拡張命令「SSE4.2」の搭載や、ロードユニットの強化といった小幅な改良が施された程度で、命令を処理するパイプラインの構造そのものはCore 2と大差ない。

ただし、Core 2の弱点だったデコーダーユニットの制約の多さを一部緩和したり改良したほか、命令群のループ構造を検出するLSD(Loop Stream Detector)と呼ばれるユニットの配置変更などにより、省電力化を図っている。 - 省電力機能の強化

- CPU内の電力供給回路周辺に、「Power Gate」と呼ばれる新開発のトランジスターを使うことで、待機電力を0に落とす機構を搭載。またC6ステートにおける省電力性を向上。

- Turbo Boostの強化

- 「Intel Turbo Boost Technology」と呼ばれる機構により、2段階の自動クロックアップによる性能向上が可能。45nm版Core 2シリーズ(Penryn)の場合、1段階のみで性能向上率も固定だった。

大雑把に言えば、CPUのパイプラインそのほかは、ほとんどCore 2と変わらないが、CPUの周辺回路を大幅に強化したと考えればいいだろう。

ちょっと厄介なのは、パイプライン構造がほぼ同一にも関わらず、上で挙げたLSDの配置換えにともなって、Core 2に最適化されたプログラムがCore i7では必ずしも最適に動かないケースが出てくることだ。これもあって、同一周波数のCore 2とCore i7を比較した場合、場合によってはCore i7がやや性能的に下回るケースも見受けられる。

もっとも、周辺回路の強化、特に大容量3次キャッシュの搭載や、3チャンネルのDDR3メモリーコントローラーの内蔵などにより、性能が底上げされているケースも少なくないので、Core 2に比べて若干高速化されている、といったところだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ