米イントリンシティ社は22日、2GHz動作の32bitMIPSベースプロセッサーとマトリックス/並列ベクトル演算ユニットを組み合わせた信号処理用プロセッサー『FastMATHアダプティブ・シグナル・プロセッサ』および、組み込み向けプロセッサー『FastMIPSマイクロプロセッサ』を発表した。この発表は日本と米国で22日付で行なわれるもので、時差の関係で日本が先の発表となっている。2002年第4四半期にサンプル出荷を開始するという。

|

|---|

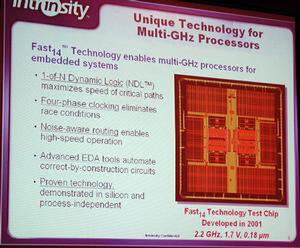

| 米イントリンシティの“Fast14 Technology”の概要と、試作したプロセッサーチップ |

米イントリンシティ(Intrinsity)は1997年設立のファブレスの半導体企業。本社はテキサス州オースチンで、マサチューセッツ州ボストンと東京に営業所を持つ。同社はダイナミックロジック回路の自動生成技術“Fast14 Technology(ファーストフォーティーン テクノロジー)”(※1)を開発した。8KBのデータ/インストラクションRAMを持つ32bitプロセッサーをFast14 Technologyを使って設計、0.18μmのアルミ配線プロセスで実際に製造し、高い歩留まりで2.2GHz動作品が得られたと2001年8月に発表している。

※1 Fast14の“14”はシリコンの原子番号を示しているという。ダイナミック回路は高速にスイッチングできるNMOS半導体を使用しており、現在ロジック回路に多く使われているスタティックCMOS回路より高速(素子レベルで3~5倍)に動作できる。しかし、ノイズ耐性が低い、信号タイミングがシビア、消費電力が比較的大きいなどの欠点を持つために、正常に動作するチップを得るまでに、サンプルチップを作ってエラーをチェックするという工程を繰り返すことになり、長い開発期間とコストがかかるため大規模な回路には向かないとされる。そのため、開発・製造しやすいスタティックCMOS回路をメインに使い、どうしても必要な部分だけをダイナミック回路で構成するという手法が一般的となっているという。

Fast14 Technologyは、ゲート遅延を低減する“1-of-N Dynamic Logic”、信号タイミングのずれを抑える“Four-phase Clocking”、インターコネクト(チップ内の配線)のノイズを低減する“Noise-aware routing”の各技術と、それら技術を組み入れたダイナミック回路を自動生成するEDAツールから成る。

『FastMATH』『FastMIPS』

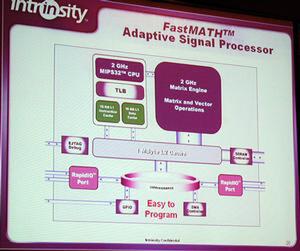

今回同社が発表したFastMATHは、医療用画像処理、ネットワークインフラのデータ処理、携帯電話基地局の信号処理、軍用信号処理用途などの、リアルタイムアダプティブ(適応性)処理分野向けのプロセッサー。FastMATHは2GHz動作のマトリックス/並列ベクトル計算ユニット、2GH動作の32bitMIPSアーキテクチャーベースプロセッサーコア、1MBの2次キャッシュメモリー、高速I/Oインターフェース(1GbpsのRapidIOポート×2)(※2)を組み合わせたことで、リアルタイム信号処理において高い性能を発揮するという。

※2 RapidIO:米モトローラ社、米ザイリンクス社などがメンバーとなっている“RapidIO Trade Association”が推進する、組み込みシステムにおけるCPUやDSP、メモリーなどの間の高速データ通信規格。 |

|---|

| 『FastMATH』の構造 |

これまでこういった分野では、ASIC(特定用途向けIC)やFPGA、DSP、デスクトップ向けプロセッサーが使われていたというが、ASICは高速処理が可能な反面、開発期間が比較的長くかかるうえにその機器専用で転用が難しい、FPGAはコストが高い、DSPやデスクトップ向けプロセッサーはマトリックス/並列ベクトル演算ユニットを持たないといった短所を持っていたという。米イントリンシティでは、FastMATHはASIC並みの高速性とプログラミング可能な処理能力を合わせ持つプロセッサーであるとしている。

|

|---|

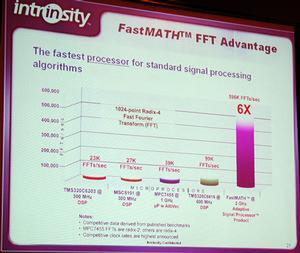

| FastMATHと、DSPや汎用マイクロプロセッサーとの高速フーリエ変換処理の比較グラフ |

同社がFastMATHと他社の最新のDSP、汎用マイクロプロセッサーを使って、高速フーリエ変換(FFT)処理速度を比較したところ、6倍以上の処理能力を発揮したとしている。また、FastMATHを携帯電話基地局のアンテナ用信号処理に利用すると、64ユーザー分の処理が2つのFastMATHでカバーできるが、これを1GHzのデスクトップ向けプロセッサーで行なうと、この6倍の数が必要だという。FastMATH自体の消費電力については明らかにしていないが、ASICやDSPなどに比べると大きなものであると考えられる。ただし、FastMATHは多数のチップを置き換える能力を持つので、システム全体の消費電力は同程度ないし低く抑えられるとしている。

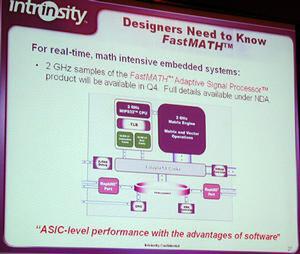

また同時に発表したFastMIPSはFastMATHからマトリックス/並列ベクトル演算ユニットを除いた、32bitMIPSアーキテクチャーベースプロセッサーコアと高速I/Oを持つ組み込み向けプロセッサーとなっている。

FastMATHとFastMIPSは、0.13μmプロセスで製造し、2GHz動作のものをハイエンドとして、複数の動作周波数のものを用意する予定。将来は4GHzまで高速化できるアーキテクチャーであるとしている。

|

|---|

| 『FastMIPS』の構造。高速I/O部分については別途発表の予定があるという |

FastMATH、FastMIPSで使用しているMIPSコアは、米ミップス・テクノロジーズ社から命令セットのみのライセンスを受け、同社が開発したコアであるという。また、FastMATH、FastMIPSの内部アーキテクチャーの詳細については現時点では非公開となっている。特に高速I/Oに関しては新しい技術を開発したということで、今後何らかの形で発表を行なうとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります