垂直トランジスタ(VCT)がもたらすDRAM構造の劇的進化

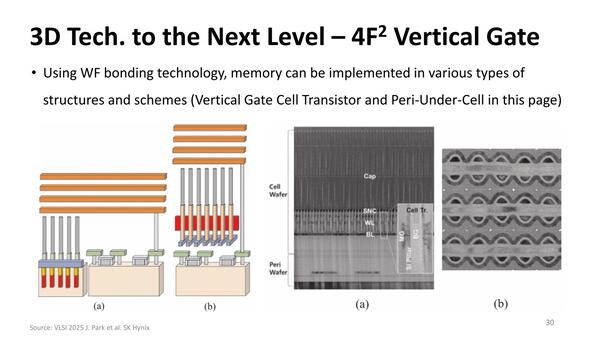

3D化で最初に思いつく技法が、WF Bondingである。これは、これまでDRAMのCell Arrayの周囲に配されていたBLSA(Bit Line Sense Amp)やSWD(Sub-Word Line Driver)などの回路を3次元実装することで、結果的にダイサイズを小型化する技術である。

もっともこの方式、ある意味お手軽ではあるし技術的にも確立しているが、明らかにコスト増になるので、一時しのぎ的な解決案でしかない。次のアイディアは4F2の実装である。

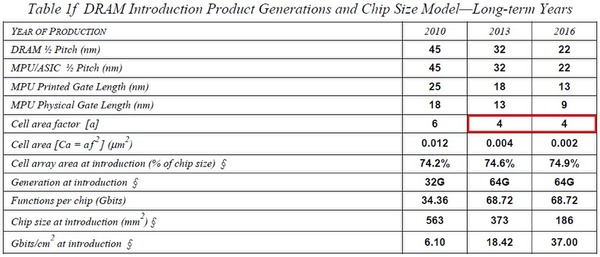

現在のDRAMの場合、F(Feature Size)に対してDRAMセルの面積は6F2になっている。例えばFeature Sizeが20nmならセルの面積は2400nm2になる計算だ。これが4F2になれば1600nm2に減ることになる。

以前は8F2という時代もあったが、現在は6F2に移行している。大昔のロードマップによれば、2013年頃には4F2に移行とかいう話だった(赤枠)が、現時点でもまだ4F2への移行は果たせていない。

実のところ2000年代からいろいろ4F2を実現するための努力はされており、2013年には"Novel 4F2 DRAM cell with Vertical Pillar Transistor(VPT)"という論文も出ていたりはするのだが、なかなか量産には至らなかった。

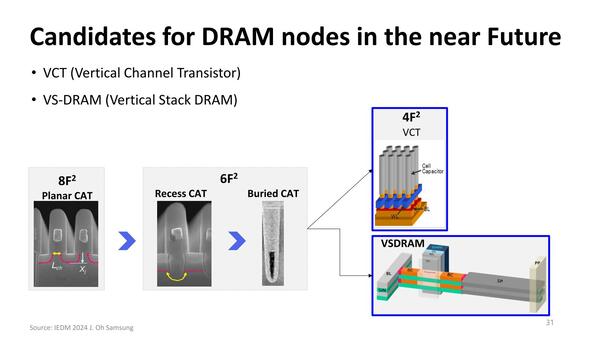

現時点で今後の世代のDRAMとして有望視されているのが、VTCを利用した4F2構造と、VSDRAMの構造である。

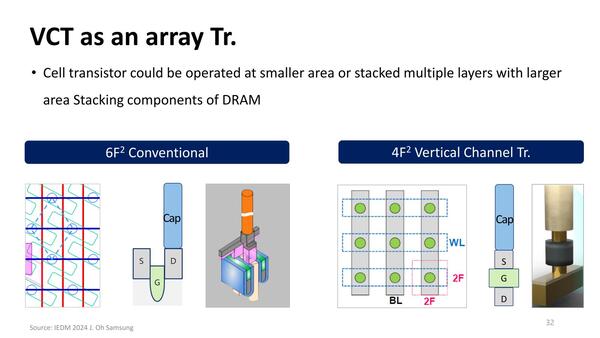

まずVCTについて。下の画像の左図が従来型のDRAMセルである。赤がBit Line、青がWord Lineで、その交点にトランジスタが配され、そのトランジスタのドレインにキャパシタが垂直に接続されている構造である。

このセルあたり1つのトランジスタが読み出しや書き込みを担当するわけだが、このトランジスタがあるがゆえに、ギリギリまで面積を詰めてもセルのサイズが6F2にしかならなかったというのが従来の限界であった。

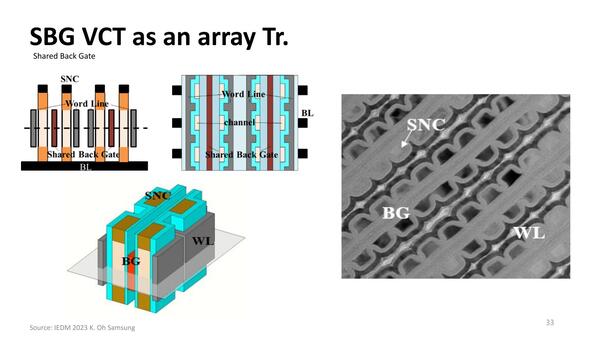

これに対してVCTでは右図のように、トランジスタそのものも垂直構造にしてしまえば底面積が4F2にできるというものである。さらに高密度化のアイディアとして、Back Gateを複数のセルで共通化するSBG(Shared Back Gate)という技法も提案されている。

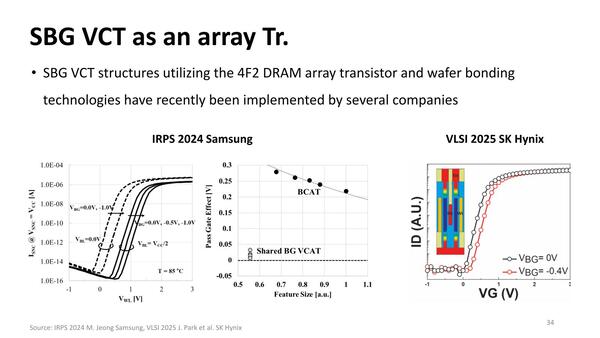

SBGを利用したVCTはSamsungとSK Hynixがそれぞれ実装例を発表している。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ