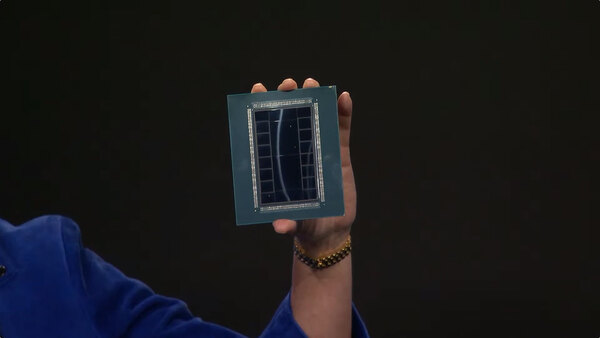

Instinct MI455Xをお披露目

GCDの上下に配されるダイが謎

最後がMI455Xであるが、こちらはVeniceよりも一回り大きい。残念ながらHBM4の正確な寸法がわからないが、仕様によれば10×10mm~14×14mmの間となっている。

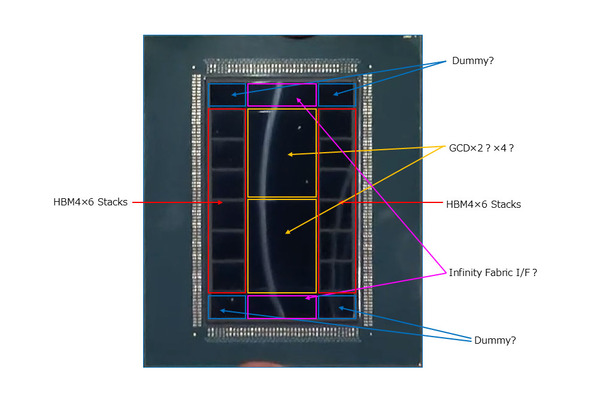

上の画像を見ると微妙に横方向が長い(11×10mmくらい?)ものの厳密な数字は出せないので、ダイサイズの推定は難しい。この写真からダイの構造を分析したのが下図である。

まずわからないのがGCD。上のダイ写真を見る限り2ダイ構成であるが、少なくとも600mm2以上のダイサイズは確実(700mm2近いかもしれない)であり、MI350Xシリーズ同様、縦方向にも切れ目が入っていて4ダイ構成の可能性がある。

それぞれのダイの左右にHBM4が3スタックずつ配置され、合計で12スタックとなる。その上下にあるのはダミーのダイな気がするのだが、問題はGCDの上下に配される横長のダイである。可能性としてあるのはインフィニティ・ファブリック(とPCIeも入っているだろう)のI/Fだが、そうなるとMI350Xシリーズとは異なり、GCDやHBM4の下にIoDは存在しない可能性が出てくる。

ただインフィニティ・キャッシュの置き場所を考えた場合、現実問題としてGCDやHBM4の下にIoDが位置する可能性は非常に高いと考えられ、するとこの端にある長いダイはなんだ? という疑問が生じることになる。これに関しても、将来AMDがもう少し情報を公開してくれないとなんとも言えないところだ。

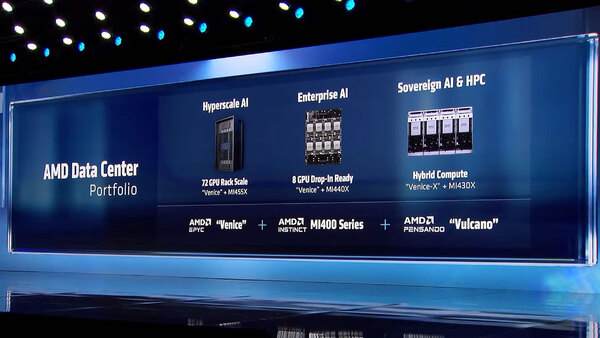

ところでこのMI400シリーズ、Helios向けにUALを併用したMI455X以外に、キャリアボードで8GPU構成のMI440X、そしてHPC向けのMI430Xの3製品がラインナップされることが公開された。

MI440Xはキャリアボードで単体動作することから、MI400シリーズには本来8本のインフィニティ・ファブリック/PCIe I/Fを持っているのかもしれない。こちらもまだまだ謎は多い。

| MI400シリーズの違い | ||||||

|---|---|---|---|---|---|---|

| MI455X | 相互接続はそれぞれインフィニティ・ファブリック×2、Veniceとの接続のみインフィニティ・ファブリック×1 | |||||

| MI440X | 相互接続にインフィニティ・ファブリック×1、ホストとの接続にPCIeで、これはおそらくPCIe Switch経由での接続 | |||||

| MI430X | MI455Xに似た構成? ただUAL Switchは持たず、Scale outのみでの接続になるかも(その分Scale out用のI/Fが強化される可能性あり) | |||||

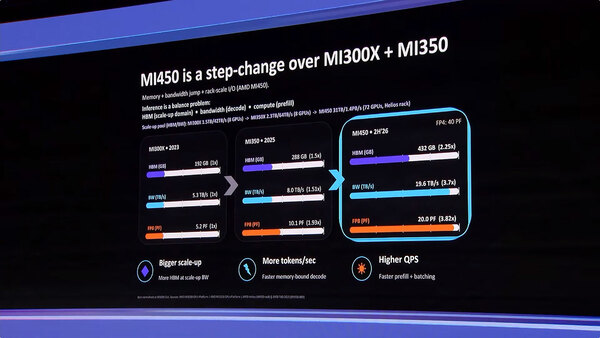

話をMI455Xに戻すと、Heliosで2.9EFlopsという数字が前ページ中ほどの画像に出ているが、もう少し具体化したものが下の画像だ。

ざっくり言えばMI350の2倍の演算性能と1.5倍のメモリー容量、2.45倍のメモリー帯域という構成になる。先の2.9EFlopsは、40PFlops×72=2880PFlopsで、丸めると2.9EFlopsという数字になるわけで、NVIDIAのRubinの50PFlops(FP4)には若干およばないものの、決して低い数字ではない。

基調講演からわかるHeliosとVenice、MI455Xの情報は現時点でこんなところである。次回はRyzen AI Embeddedについて解説したい。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ