NanosheetはForksheetより電流を小さくできる

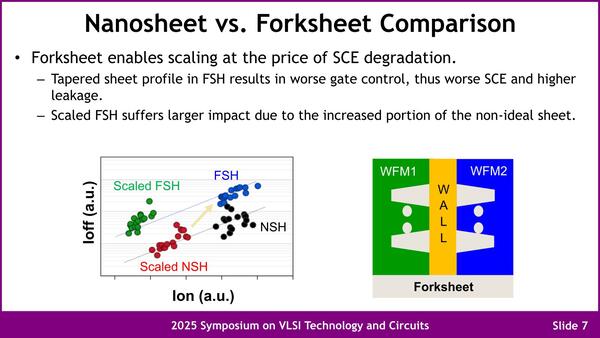

NanosheetとForksheetの違いについて説明しよう。Nanosheetの場合は、Sheetの厚みが均一になる(というか、均一になるように作っている)のに対し、Forksheetの場合は根本(誘電部となるWall)の根元がやや太いテーパー状になってしまう関係でゲート制御がNanosheetよりも難しく、結果としてSCE(Short Channel Effect)が悪化する。

左のグラフがそれで、NanosheetはOffにした時に流れる電流(Ioff)が基本的にはForksheetより少ないというか、ForksheetにするとIoffがNanosheetに比べて増える、というのが正しい表現なのだろう。

加えて幅を狭めた場合、今度はIonにおける電流値が減る。結果から言うと、幅を狭めたForksheet(Scaled NSH)の特性は、もともとのNanosheet(NSH)と比べ、「Ioffの電流は大して変わらず、それでいてIonの電流が大幅に減る」という、単に性能が悪化したトランジスタになってしまうことがわかる。

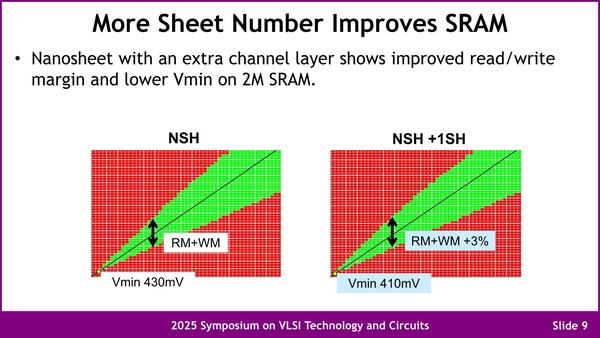

ただ特性に関して言えば、下の画像で示すようにNanosheetではSheetの数を増えすだけで(Ioffを増やさずに)Ionを増やせる(左グラフ)ほか、Forksheetの場合はデバイスの静電容量はむしろNanosheetより減らせる(右グラフ)というメリットもある。

ちなみにSheetを1枚増やすことで最小動作電圧が20mV下げられるほか、定格(RM+WMの矢印がある電圧)では、動作マージンが3%増えるという形でトランジスタの動作特性が改善されるというメリットもあるとする。

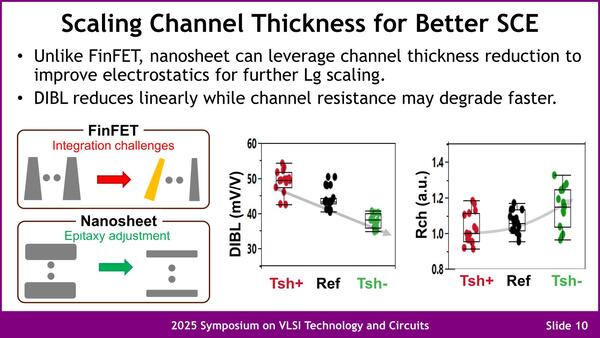

話は変わるが、NanosheetがFinFETより有利(?)なのは、薄型化が容易なことだ。エピタキシー(基板上に薄膜を形成する手法)で厚みを楽に調整できるので、FinFETのように薄くしたら倒れたり、折れたりすることにはならない。

もっともSheetの数だけエピタキシーの工程を入れる必要があるので、手順そのものはFinFETより大幅に増える可能性があるので、工程全体で考えるとあまり楽ではないのかもしれないが。

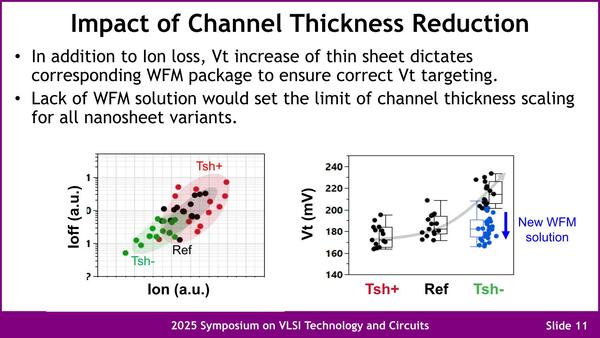

それはともかくNanosheetを利用する場合、Sheetの厚みを薄くすることでDIBL(Drain Induced Barrier Lowering:ドレイン誘起障壁低下)の電圧を下げられるメリットがある一方、チャネル抵抗そのものの増加と、量子閉じ込め効果(Quantum Confinement Effect)に起因するVtの上昇はトランジスタの劣化を加速させる。

これを避けるために、デバイスのパラメーター調整、それと新しいWFMの解決策が必要とTSMCは論じている。

Forksheetはテーパー具合を軽減できれば性能が改善する

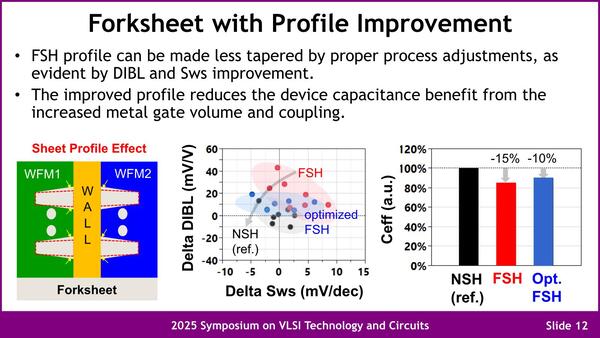

ここで再び話がForksheetに戻ってくる。Forksheetの特性がNanosheetより悪化する理由の1つは、間にWallを挟むと、Sheetがテーパー状になってしまうことに起因する。であれば、それを完全になくすのは無理にしても、そのテーパー具合を軽減できれば性能が改善する、としている。

FSHをどう作るかにもかかっているのだが、従来(例えばimecが2020年のIEDMで講演した方法)ではまずNanosheetを(NFET/PFETとまとめて)構築した後で、Wallの部分を削ってそこに誘電材を埋め込む形となる。ここでどうテーパーを減らすかに関しての説明は今回はなかった

具体的には、DIBLを10~20mV/V程度減らし、それでいて静電容量の増加は最小限に抑えられるとする。おもしろいのはテーパー構造になっているForksheetの方がやや静電容量が低いことで、これはゲート制御を回復するためにWMFの体積が増えることになり、これが静電容量増加をともなうためとのことである。

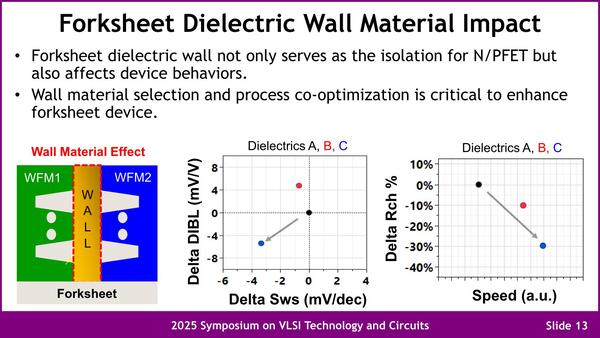

ForksheetのWallの材質もまた性能に影響を与えるとしている。当然ながら誘電材料として具体的になにを利用したのかに関する説明はないのだが、とりあえず誘電体A/B/Cという3種類の材質によって特性が変わることが示されている。

上の画像のグラフは特性の一例であるが、特性はこれ「だけ」ではないので、さまざまな特性の変化を見ながらのトレードオフが重要ということを示しているとする。

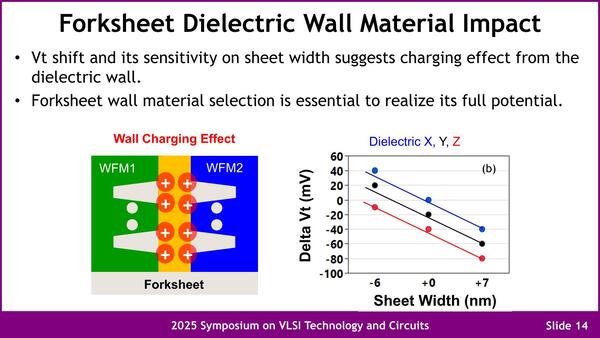

この材質に関してで言うと、材質とSheetの幅が、Vtの変動に大きな影響を与えていることも判明しており、実際左で言うと幅を6nmほど詰めるとVtは40mV近く向上、逆に7nm広げると40mVほど低下するとしている。

つまり幅を広げるほど効率の良い動作が可能であるが、ただしトランジスタの密度は下がるのでここもまたトレードオフということになる。このVtが変動する理由は、ForksheetのWall部分に発生する電荷の変動である。WallとChannel、それとS/Dが近接している関係で、絶縁材料内部の固定電荷が変動するというわけだ。

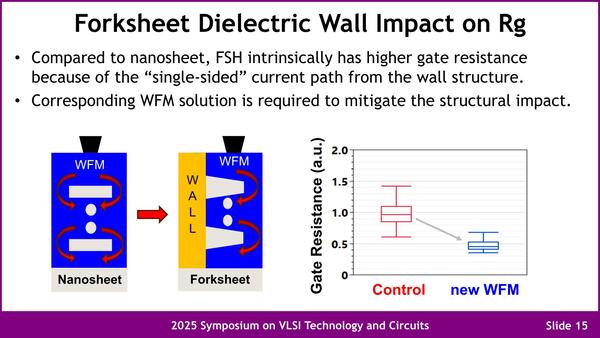

それとNanosheetに比べて、Forksheetの場合は構造的にゲート抵抗が高くならざるを得ない。この影響を改善するためにも、より改善されたWFMが必要としている。

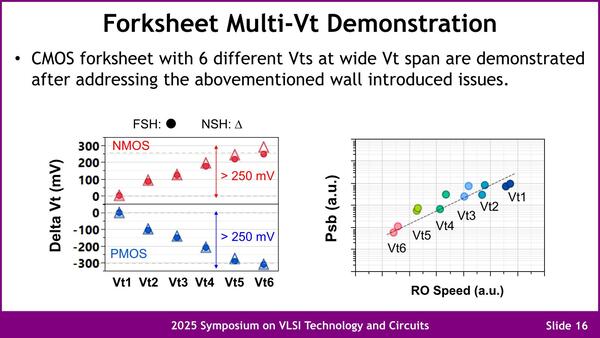

こうした問題はあるものの、すでにForksheetを利用しての6電圧での動作が可能とされ、その電圧差は250mVを超えている。これにより、用途に応じた電圧(と動作周波数)を選んで利用することがForksheetでも可能としている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ