帯域不足がCSA誕生のきっかけ

そんなCSAであるが、フタを開けてみると単にGbE用のI/Fということが明らかになったわけだ。なぜ専用I/Fを設けたか、これは単純に「PCIのまま接続すると帯域が足りないから」である。GbE、つまり1000BASE-TはIEEE 802.3ab-1999として1999年7月に仕様が公開されたが、公開当初はまだ高嶺の花であった。

2000年頃には、まだGbEの拡張カードは64bit PCIで提供されていた(例えばプラネックスの「GN-1000TE」など)し、GbEのハブ(まだSwitching HubではなくDumb Hubだった)も高価だった。

ところが2002年頃からこうした製品の価格が次第に下がり始める。一般的にイーサネットの場合、ポート単価が100ドル(だいたい体感で1万円前後)を切り始めると急速に普及が進む感じだが、これが2002~2003年頃に発生し、以後はそれまでの100BASE-TXに代わり1000BASE-Tが実装されるようになってきた。

例えば2002年9月末には、Broadcomの1000BASE-Tコントローラーを搭載したMSIのマザーボードが秋葉原に登場している。したがって2003年は本格的にGbEが普及する年となることが予想され、事実そうなった。

問題はこれがPCIだと帯域が足りないことだ。というのは1000BASE-Tでは1000Mbpsの全二重、つまり上り下りとも125MB/秒の帯域を持つので、32bit/33MHzとなるPCIの133MB/秒では帯域が全然足りない計算になる。上で初期の1000BASE-Tのカードが64bit幅になっていたと書いたが、これは64bit/33MHzでは266MB/秒の帯域になり、これならGbEの帯域にマッチするから、という話である。

しかし通常のマザーボードには64bitスロットが搭載されていないので、ユーザーからするとこれが問題となる。もちろん64bitのカードを32bitスロットに装着可能だが、その場合は32bitでの転送となるので帯域は133MB/秒となり、帯域が足りない計算になる。

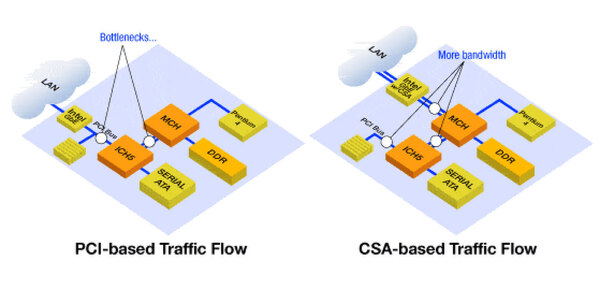

インテルからすると、事態はもう少し深刻だった。下の画像がこれを簡単に示したものだが、もしPCIバスの先にGbEコントローラーを直接接続してしまった場合、GbEが動くとPCIの帯域のみならずHubLink(MCHとICH)の帯域も飽和してしまうため、他のI/Oが動作しなくなる(逆に他のI/Oが動作中はGbEがフルに動かなくなる)という問題が予想されることになった。

例えばイーサネット経由でインターネットなどからコンテンツをダウンロードする場合には、以下の行程が同時に発生する。

(1) GbEからICH→MCH→メモリーという順にコンテンツを一旦メモリーに格納

(2) 格納した内容をメモリー→MCH→ICH→Serial ATA経由でHDDに保存

この場合は、以下の問題が発生することになる。

- PCIはGbEからの読み込みでほぼ使い切ってしまう。

- HubLinkは、Intel 800シリーズチップセットではHubLink 1.5(266MB/秒)を利用しているのでPCIよりはゆとりがあるが、それでも上りと下りの両方が同時に発生する関係でやはり帯域を使い切ってしまう。

解決法は簡単で、例えばICHにPCIのコントローラーを2つ搭載し、HubLinkもより広帯域なものに変更すれば済むわけだが、当時インテルは続くIntel 900シリーズチップセットでPCI Expressの全面導入を予定しており、この時期に無駄にICHにまで手を入れたくなかった、という事情があった。Intel 900シリーズで内部を全面改訂するのに、その前にMCHとICHを大変更、というのはインテル的にもあまりうれしくなかったのだろう。

思うに、2000年頃にはもう当然2005年頃までの大まかなロードマップが決まっており、この時点でPCI Expressは2004年に導入される(それ以上前倒しはできない)一方、GbEが2003年頃に爆発的に普及するので、チップセット側で対策をしなければならないという状況が見えていたのだろう。

そこでPCI Expressが登場するまでの1年間のピンポイントリリーフとして考え出されたのがCSAだった、と思われる。理屈は簡単で、MCHの側に追加のHub Linkを用意し、これをGbE専用とすることだ。この場合、先のコンテンツダウンロードでは次のようになる。

(1) GbEからMCH→メモリーという順にコンテンツを一旦メモリーに格納

(2) 格納した内容をメモリー→MCH→ICH→Serial ATA経由でHDDに保存

Hub Linkを占有する帯域は半分に減るし、PCIは完全に開放されるので他の入出力を実行可能である。しかもこの方式ならICHは原理的に従来のものをそのまま利用できる。

実際にはIntel 865/875シリーズと組み合わされるのはICH5で、これは2002年にIntel 800シリーズ(Intel 845E/G/GV/GL/GE/PEとIntel 850E)にあわせてリリースされているICH4から変更されてはいるが、主な違いはUSB 2.0ポート数(6→8)とSerial ATA I/Fの統合、ACPI 2.0への対応などがあり、パッケージも大型化してはいる。したがって「従来のものをそのまま」というのは厳密には語弊があるのだが、技術的にはICH4から大きく差はなく、比較的スムーズな移行が可能だった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ