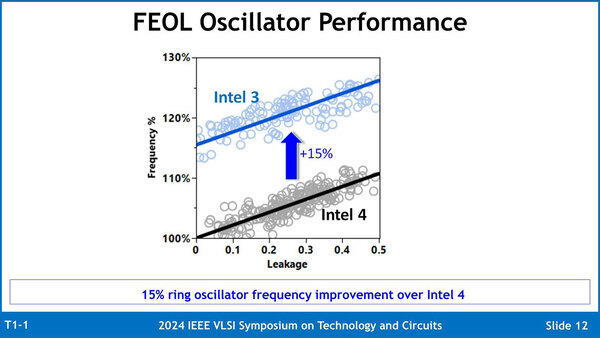

同じリーク電流なら動作周波数が15%ほど向上する

次にFEOL、つまりトランジスタ層の話である。OverallとしてRing Oscillatorを構成した場合の動作周波数は、同じリーク電流なら15%ほど動作周波数が向上するとしている。

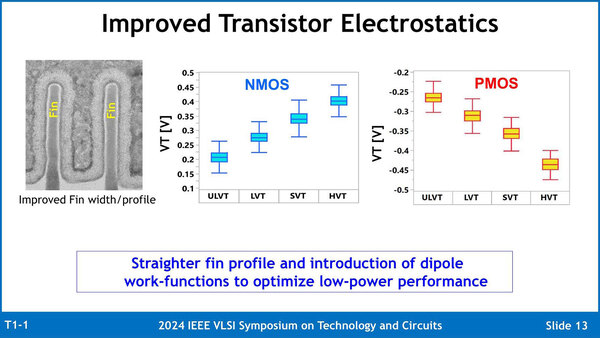

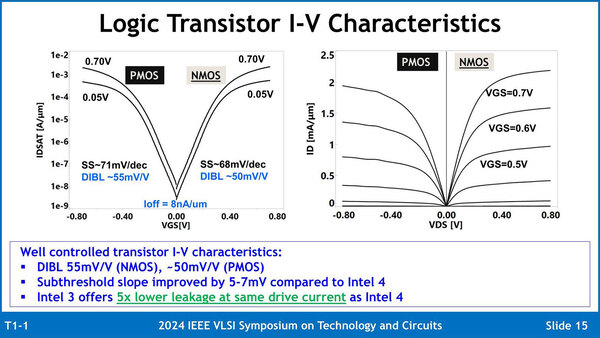

もう少し細かなトランジスタ特性が下の画像だ。

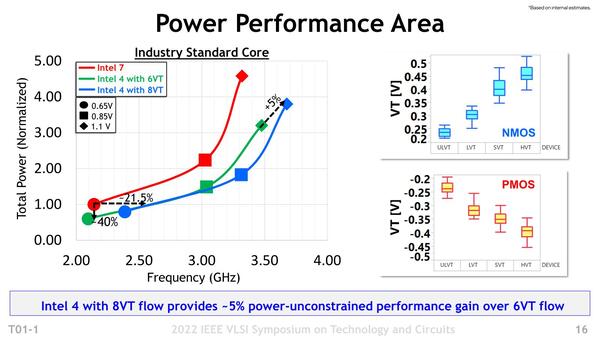

Intel 4の時の特性が下の画像であり、ULV~HVTまですべてのケースでより動作電圧が下がっていることが見て取れる。

これが実現できた理由は、Finの形状を工夫してより特性を向上させた(以前はFinの形状が末広がりだったのが、もう本当に横から見ると棒という感じになっている)ほか、コンタクトの接合方法を工夫したことだとしている。

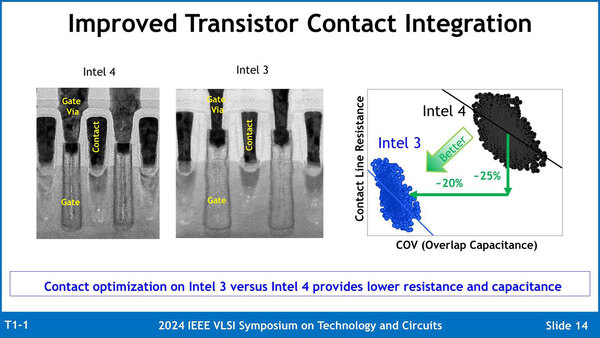

そのコンタクトの接合方法に関するスライドが下の画像である。Gate ViaやGate、Contactの周囲の絶縁層がより広く取られている。その一方でGate ViaとGateの接続部は、Intel 4よりもよりしっかりと接続されているのがわかるかと思う。

この断面写真で見る限り、Gateの接続部はGateがGate VIAを包み込むように接続されているように見える。Intel 4では水平面で接続されているが、Intel 3では側面まで使って接触面積を増やしたようだ

結果として、Intel 4→Intel 3で接続部の抵抗(Contact Line Resistance)が25%、全体の寄生容量(Overlap Capacitance)が20%削減されたとしている。これだけ配線部の抵抗や容量が減ったら、それは特性の向上に大きな寄与が見込めるだろう。

このContact Gate周りの工夫やFin構成の改善のほかにもいくつか改良点はあるのだろう。結果としてトランジスタの特性もだいぶ改善された。

トランジスタの特性。Ioffはトランジスタがオフの時に流れる、要するにリーク電流を示しており、Intel 4では20nA/μmとされていた。したがってリーク電流そのものは5分の2になる計算だが、それが5分の1というのはゲートの寸法も変わっているということだろうか

Intel 4の場合、Short Channel EffectsはPMOSがSS:~75mV/dec、DIBL ~77mV/V、NMOSが75mV/dec、DIBLは~62mV/Vだった。SS(Subthreshold slope)も、DIBL(Drain-induced barrier lowering)も、それが大きいほど大電圧をかけた際の性能低下が大きくなる。このあたりも性能改善(特に高速動作時の消費電力を抑えること)に貢献しているものと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ