ロードマップでわかる!当世プロセッサー事情 第737回

Sierra Forestの内部構造はGracemontとほぼ変わらない インテル CPUロードマップ

2023年09月18日 12時00分更新

Sierra Forestのダイサイズは

Emerald Rapidsと同程度

構成を定めたところで、次は寸法の推定である。まずPコアとEコアの寸法比だが、連載688回のスライドはさすがに荒すぎて推定に使うのも厳しすぎる。と思ったらWikipediaのRaptor Lake(英語版)に、Core i9-13900Kのダイ写真と、それをブロック分けした写真が掲載されていた。

幸いCC0ライセンス(著作権による制限を受けないで再利用できる)での提供なので、遠慮なく使わせていただいたのが下の画像である。

面積比率で言えばPコア×1+3MB LLC:Eコア×4+4MB L2+3MB LLC=1:1.248といったところ。Eコアの方が幅は広いがやや高さが少ない感じである。4つのEコアと2次キャッシュに挟まれた部分が少し面積を取っている(おそらくL2/L3のコントローラー部と思われる)のでやや幅広になっている感じで、これをもう少し再設計して最適化すれば幅がもう少し減るように思うが、それはともかくこの数字をそのまま使うと、Intel 7でこれを構築した場合には13.18×1.248=16.45mm2といったところ。

これを36個集積すると592.2mm2になる。実際にはさらにメモリー・コントローラーが入るので658mm2くらい。それにPHYの分など(DDR5が8chと、あとEMIB経由でI/Oチップレットを接続するための内部のメッシュのPHYが8対なり10対必要になる)があることを加味すると、750mm2といったところか。要するにEmerald Rapidsと同じ程度のダイサイズになることが想定される。要するに、ギリギリ1チップテットでも実装できそうというわけだ。

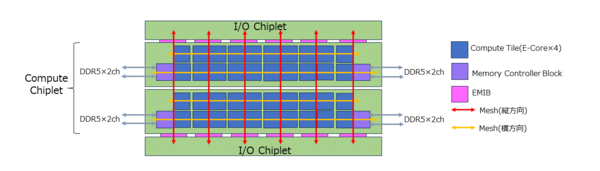

では2/3チップレットの可能性はあるか? まず2チップレット。これでも必要量なブロック数は1チップレットの場合と同じで、合計40ブロック。2つなので20チップレットになる。

これでは少し無駄が出るが各チップレットあたり12ブロックで、うち2つは空き(もしくは冗長ブロックにする?)とする上図のような方式だ。これなら12ブロック分の面積は395mm2ほど。周囲のPHYの分を加味しても500mm2程度で収まり、だいぶ製造の容易度が上がる。

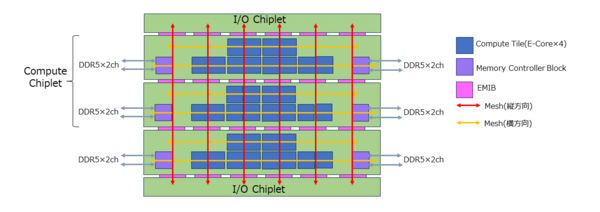

さらに無駄が多いのが3チップレット。こちらでは必要ブロック数がEコア×4のブロックが36とメモリーコントローラーが6ブロックになり、42ブロック。これを3で割って14ブロックとなる。これは下図のような構造になることを意味する。これならば、チップレットの大きさは2チップレットの場合と変わらず500mm2程度にしかならない。

経済合理性を考えれば3チップレットという選択肢はあり得ない。2チップレットはまだ現実的だが、それなら空きブロックも全部コアを入れることでEコア×4を40ブロック、トータルで160コアの製品にするだろう。逆に言えば144コアしかない、という時点で1 チップレット構成であることが事実上確定したようなものである。

つくづくインテルは大きなダイサイズの製品を作るのが好きだなと思わざるを得ない推定結果に終わった。さて、間もなくIntel Innovationが開催されるが(この原稿は開催前に書いている)これに関する情報が出てきて筆者の推定の答え合わせができるだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ