5月18日、インテルは突然Advanced Packagingと題した説明会をオンラインで開催した。タイミングとしては突飛というか、なぜこの時期にこのテーマを? となるし、初めて聞く話はないのだが、それでも以前からの疑問がいくつかクリアになったので説明しよう。

ちなみにインテルのパッケージング技術は、連載627回のほかに、連載682回にHotChipsでの発表をベースに紹介しているので、これらからの差分という形での説明となる。

連載682回の時点ではまだ第2世代Foverosに関しては量産製品は存在していなかったのだが、今年1月にPonte VecchioがIntel GPU Maxとして発売になったことで、Bump pitch 55μm EMIBと36μm Foverosの組み合わせ技もちゃんと量産できることが実証された格好になる。

ちなみにLakefieldに使われた第1世代のFoverosのBump Pitchは50μmであり、36μmはIntel GPU Maxが最初ということになる。その次がMeteor Lakeというわけだ

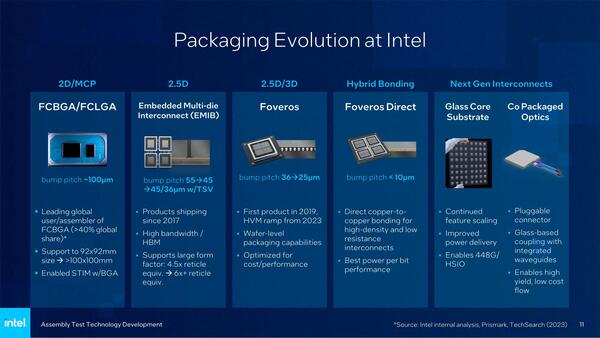

さて、ここからの話が若干のアップデートである。下の画像がそのアップデートの項目だ。

(1) FCBGA/FCLGAパッケージの寸法が最大92×92mmから100×100mmに拡大

(2) EMIBはBump Pitchの微細化ロードマップが55μm→45μm→36μmに変わり、36μm世代ではTSVが利用できるようになることが明らかにされた

(3) FoverosはBump Pitchが36μm→25μmになるとされた

(4) Foveros Directの第2世代はBump Pitchが9μmになると明らかにされた

(5) 次世代パッケージとしてガラスベースのSubstrate、およびCo-Package Opticsが提供される(予定)

基板のパッケージサイズを順次大きくしていく

順に見ていくと、まず(1)のFCBGAの話だが、基板のパッケージサイズを今後100×100mm以上に引き上げられるとしている。もっともこれは一気にではない。まず2024年にこれまでの56×100mmという寸法を92×92mmまで拡張、また配線層を従来の24層から26層に引き上げるとする。次いで2026年にはこれを100×100mm超に拡張するという形だ。

この92×92mm、という数字はEMIBでも出てくるあたり、2024年度に向けて新しい製造装置を導入、これが92×92mmに対応ということなのかもしれない。

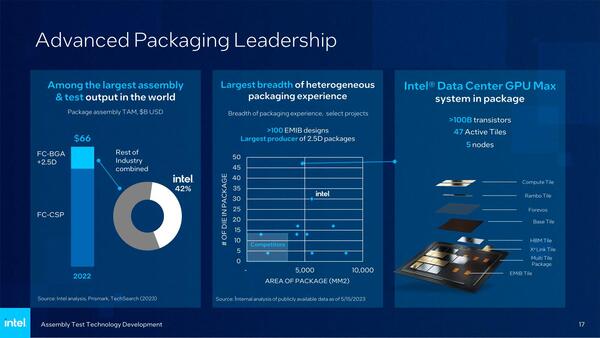

余談だが、インテルはこのFCBGA/FCLGAパッケージのシェアで4割を超えており、業界トップであるとしている。もっとも同社の提供しているFCBGA/FCLGAのBump Pitchはおおむね100μm程度なので、AMDがRadeon RX 7000シリーズの接続で利用できるレベルか? というと少し怪しい。

インテルはこのFCBGA/FCLGAパッケージのシェアで4割を超えている。後でも出てくるが、このFCBGA/FCLGAのパッケージはプロセスノードや製造するファウンダリーと無関係に利用可能で、このパッケージ製造だけを受託するビジネスが盛況であるとしている

さらに余談になるが、昨今OSAT(Outsourced Semiconductor Assembly & Test:要するに後工程の処理)を担うベンダーの技術開発もすさまじい。というのは、CoWoSでもEMIBでも良いのだが、シリコン・インターポーザーを使ってダイ同士を接続する方式が流行ってしまうと、こうしたシリコン・インターポーザーはそれこそTSMCだったりSamsungだったりUMCだったりインテルだったりといった、前工程を製造するファウンダリーが手掛けている関係で、ここの部分をファウンダリーに持っていかれてしまうことになる。

そこで、従来のオーガニックパッケージを使いながら、シリコン・インターポーザーに負けないBump Pitchと配線密度を実現する、といった解決策を打ち出し始めており、Radeon RX 7000シリーズもこれを利用した格好だ。

インテルは、今後もFCBGA/FCLGAパッケージ市場で存在感を維持したければ、こうした動きに対抗していかなければいけないわけだが、これはEMIBと思いっきりぶつかるという話でもあるので、このあたりをどういう方針にするつもりなのか興味ある部分だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ