今回は毛色を変えて、EUV(Extreme UltraViolet:極端紫外線)を説明しよう。昨今EUVをどこまでモノにできるか、というのがファウンダリー各社の焦点になっているのはご存じのとおりで、IBMと提携して2nmプロセスでの製造に突き進む日本のRapidusも、なるべく急いでEUVプロセスを習熟する必要がある。

この話そのものは別にいまさらという内容ではあるのだが、3nmから先になるとそのEUVでもダブル・パターニングが必須になるといった状況に加え、ここにApplied MaterialsがSculptaと呼ばれる新しいシステムを発表したことで、いろいろと憶測が飛んでいる状況にある。

EUVの話はだいぶ昔(2014年)にしたが、これはまだEUVの量産が始まる以前の説明であり、もう量産機が大量に稼働している現在とはまた状況が違う。そんなわけで、今回はEUVによる露光プロセスを説明したい。

ウェハーを感光させて回路パターンを作る技術

露光とはなにか? だが、そもそもLSIの製造手法は連載238回で説明したとおりだ。まずウェハーを洗浄した上で酸化膜を作り、さらに回路層を構成する材料の膜も作る。ついで、感光材(光が当たると変質する素材)と呼ばれるものを塗る。

それを塗り終わったら、上から回路パターンを模した「マスク」というものを挟んで光を当てる。これを行なうことで、回路パターンの部分には光が当たらず、パターンがないところは光が当たる。光が当たったところは感光材が反応して変質する。

この後で定着(銀塩写真の現像にあたる処理)を行なうことで、パターンがある部分がしっかり残る。この定着が終わったらエッチング(パターンのない部分を溶かす処理)を行なうことで、回路パターンがウェハー上に定着するというものだ。

もう最近は滅多に聞かないが、サンハヤトなどが出している感光基板を使ってプリント基板を自分で作ったことがある方なら、このあたりの手順をよくご存じのはずである(*1)。

話を戻すが、この露光が問題になってきたのは、回路パターンがどんどん小さくなってきたためである。このあたりの話は連載252回でも触れたが、なにしろ先端プロセスではトランジスタを構成するゲートの幅も、配線の幅も大幅に短くなっている。

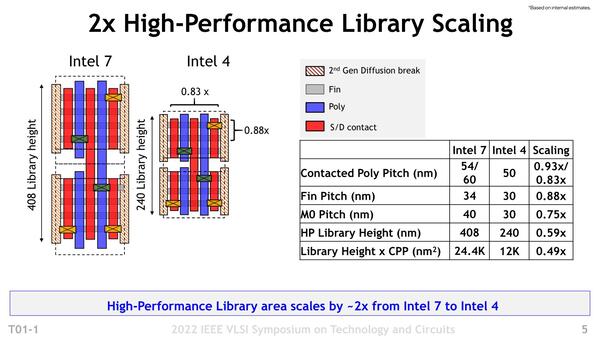

Intel 7とIntel 4でのゲートの幅や配線の幅は連載675回で紹介しているが、ここでContacted Poly Pitchが要するにゲートの幅、M0 Pitchというのが一番狭い部分での配線の間隔(幅はこれよりさらに狭い)になる。ここでなにが問題になるかというと「光の波長が、必要とされるものより大きい」ことである。

光はその種類によって波長が決まっているのはご存じのとおり。連載252回でも書いたように、もともと使われていた高圧水銀ランプだと436nm、KrF(フッ化クリプトン)のエキシマレーザーで248nm、ArF(フッ化アルゴン)エキシマレーザーで193nmとなっている。

他にF2(フッ素)エキシマレーザーが157nmで、これもずいぶん有望視されていたのだが、開発に手間取っている間に液浸の手法が出てきてしまったので、ほとんど使われていない。

実際はこの436nmなり193nmなりをそのまま当てはめるわけではない。解像度と一般に呼ばれるが、これは下の公式で計算される。

解像度=K(プロセス係数)×λ(光源の波長)÷NA(レンズの開口数)

このうちKは処理系に起因する要因(感光材の品質や軸外照明といった解像度工場技術など)で決まるもので、理論上の最小値は0.25だが実際には0.3くらいが限界(これも実は結構厳しい)。λは先に説明した通り、露光に使う光の波長である。

そしてNAであるが、上図のような構図を考えた際に開口数NAは

NA=sinθ

となる。つまりNAの最大値は1.0であるが、実際にはそこまで行くことはない。光源とウェハーを近づければ近づけるほど1.0に近くなるわけだが、限界があるからだ。

実際ASMLのDUV露光機のDry systemsに挙げられている例は以下のとおり。

| DUV露光機とNA値の関係 | ||||||

|---|---|---|---|---|---|---|

| 機種 | NA値 | |||||

| TWINSCAN XT:400L | 0.65 | |||||

| TWINSCAN XT:860M/860N/870 | 0.80 | |||||

| TWINSCAN XT:1060K/1460K/1470 | 0.93 | |||||

このTWINSCAN XT:1060K/1460K/1470を使って、光源には193nmのArF(フッ化アルゴン)を採用したとすると、解像度はKが0.25なら51.88nm、0.30なら62.26nmほどになる。実際には下表が発表されており、それぞれKの値が0.38/0.31/0.27程度になっているものと考えられる。

| DUV露光機と解像度の関係 | ||||||

|---|---|---|---|---|---|---|

| 機種 | 解像度 | |||||

| TWINSCAN XT:1060K | ≦80nm | |||||

| TWINSCAN XT:1460K | ≦65nm | |||||

| TWINSCAN XT:1470 | ≦57nm | |||||

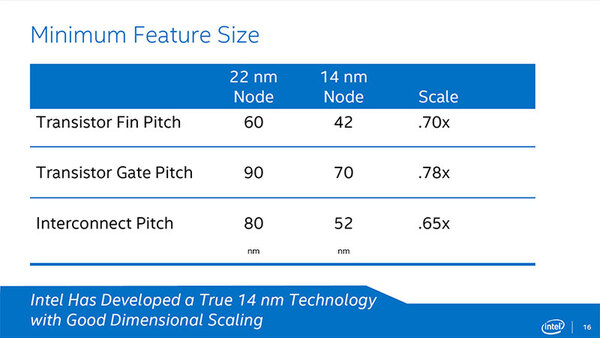

ただ一番解像度の高いTWINSCAN XT:1470でも57nm程度が限界である。以前インテルの22nmと14nmの比較を示したが、このままでは14nmの製造はとても不可能である。

(*1) 最近は基板CADでプリント基板の設計をした後、そのデータをプリント基板製造業者に投げて製造してもらうのがかなり手軽になってしまったし、CNCを持っている人はCNCを使って基板を作るという技もあるので、個人で感光基板を利用するニーズはかなり減ってしまった模様だ。サンハヤトの感光基板製作入門キットも、「在庫限り」になってしまっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ