今回お届けするのはSyntiantである。Syntiantは2017年に創業しているが、2018年には早くも最初のプロセッサーシリコンを出荷開始しており、出荷開始後1年半で100万個、2021年1月の時点では1000万個の製品出荷を達成している。

Syntiantの創業者はJeremy Holleman博士(現Chief Scientist)、Kurt Busch氏(現CEO)、Pieter Vorenkamp氏(現COO)とSteph Bailey博士(現CTO)の4人。

このうちVorenkamp氏とBailey博士は2006~2016年の間Broadcomに在籍(Vorenkamp氏はSVP, Operations Engineering/Operations & Central Engineering、Bailey博士はSenior Technical Director)だったのでまだつながりがありそうなのはわかるが、Busch氏はDECやインテル、ADI、Mindspeedなどいくつかの半導体企業を渡り歩いた後で、2015年まではIoT機器を手掛けるLantronixのCEOを務め、その後自身で興したBusch Toschi, LLCというテクノロジー企業向けビジネスサポートの会社を経営していた。

もっと関りがわからないのがHolleman博士で、Syntiant参画前はノースカロライナ大の准教授である。もっともそのHolleman博士は超低消費電力な回路のエキスパートでもあり、実はSyntiantのコアテクノロジーはHolleman博士によるところが多そうにも見える。

Busch氏はテクノロジー企業の経営エキスパートという立場であり、Vorenkamp氏とBailey博士がビジネスの種を思いつき、Holleman博士を引き込んでテクノロジーを確立。そこでBusch氏に相談を持ちかけて起業、というあたりがありそうなパターンに見えるが、そのあたりの詳細はまだ定かではない。

NORフラッシュを使いアナログベースのMACエンジンを構築

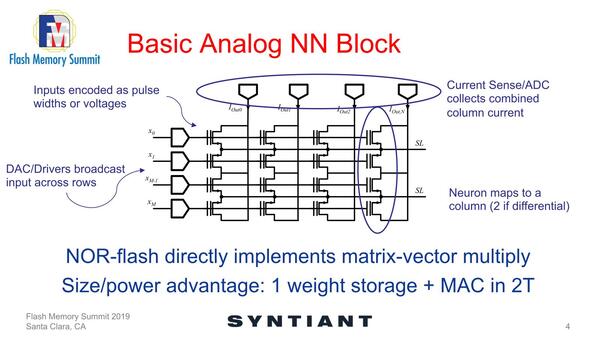

さてそのSyntiantのコアテクノロジーであるが、実は理屈は連載591回で紹介したMythicのものに良く似ている。マトリックス配置にしたフローティング・メモリー・セルに、あらかじめウエイトを保持しておく。その状態で入力された値をDAC(Digital Analog Converter)経由で、入力した値に比例する電圧の形でかけてやると、フラッシュに保持されたウエイトに比例する形での電流が流れる。これをまとめて測定することでMAC演算ができるという仕組みだ。

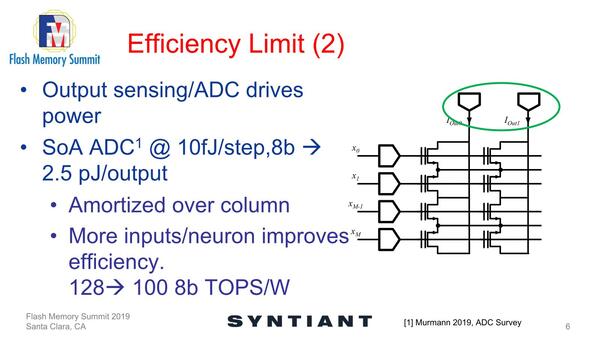

こちらは2019年のFlash Memory Summitで公開されたもの。連載591回のスライドと上下方向は逆だが、基本的に同じである

このマトリックスになったフラッシュメモリーというのは、実はNORフラッシュそのものである。NANDフラッシュとNORフラッシュの違いは連載259回で説明したが、要するにBit Line(上の画像で言うなら縦方向の配線)がセルごとに用意されているのがNOR、複数のセルをまとめて1つのBit Lineで済ませているのがNANDである。

NORはこの結果としてbit単位でフラッシュメモリーのセルにアクセスできるのに対し、NANDはブロック(これは製品によるが、KB~数十KB単位)でのアクセスしかできない。もちろんその分配線が減るので、フラッシュメモリーのセルを高密度に実装でき、結果として容量増大につながっているわけだが。

話を戻すと、Syntiantは要するに普通のNORフラッシュを使い、Bit Lineに電流検知回路を組み込むことで、Mythicと同じようにアナログベースのMACエンジンを構築したわけだ。

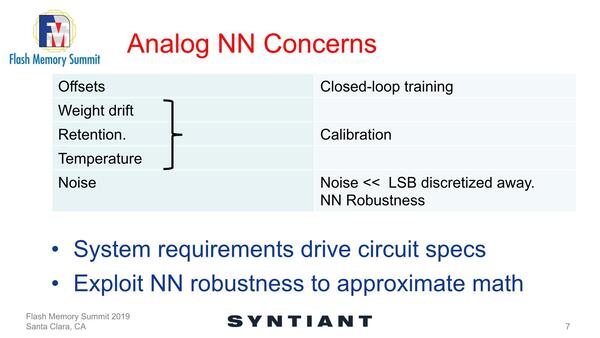

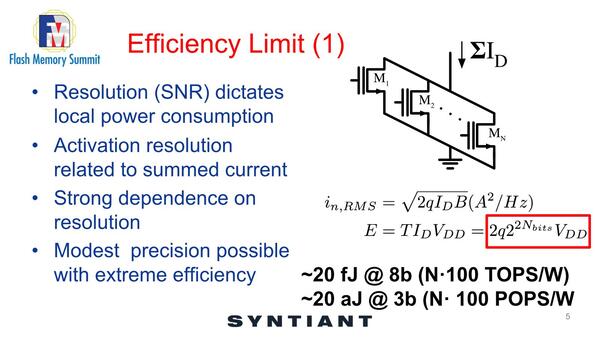

さて、この方式が回路構成的に有利なのはMythicの例でも明らかなのであるが、もちろん欠点というか問題がある。それは主に精度である。まず解像度とSN比の関係だ。

当たり前ではあるのだが、精度を高くとろうとすると、フラッシュメモリーセルにかける電圧(上の画像で言えば、左側からDACを経由してかかる電圧)を高くした方が良い。その一方で、電圧を上げると当然消費電力も増える。したがって、どの程度の精度が必要かをきちんと見極める必要がある、という話である。

Syntiantの試算では、8bit精度を保つ場合は1回の演算(というのが正確かわからないが、フラッシュメモリーセルに電圧をかける処理)の際の消費電力は20fJ程度と試算されるのに対し、3bit精度まで落とすと20aJ(=0.02fJ)と1000分の1に削減できるとする。

8bit精度を保つ場合は1回の演算の際の消費電力は20fJ程度だが、3bit精度まで落とすと20aJになる。ちなみに、fJ(フェムトJ:10^-15J)も珍しいが、aJ(アトJ:10^-18J)はもっと見かけない

次が出力のADCの解像度である。ADCはDACの逆で、電圧を検出してこれをデジタル値で出力する。電流量の検出なのに電圧検知なのか? と思われるかもしれないが、電圧を直接検知するのは難しい。ホールセンサーなどもあるが、あれも実は中でホール素子と呼ばれるものを利用して電流に比例した電圧を検出しているのでやはりADCが使われる。

ADCの詳細。実はこのBoris Murmann博士の2019 ADC Surveyを見ても、SoA ADCなるものが出てこない。最新版でも不明である。SAR ADCの間違いだろうか?

そこで電流から電圧を検出し(これはオームの法則で簡単に実装できる)、その結果をADCで取り込むことで結果的に電流値を検出するわけだが、当然だが0.1Vを8bit(=256段階)に区別するより1Vや10Vを区別する方が容易で、誤差も入り難い。したがって、電圧を上げた方が効果的ではあるのだが、これはそのまま消費電力増に直結する。

ここでまた精度と消費電力のバーターになるわけだが、ちょっとした抜け道がある。このADCで検出するのは、畳み込み演算の最後の部分、つまり加算を行なう部分にあたる。加算するフラッシュメモリーセルの数が多くなればなるほど、合計の電流量(=ADCで検出する電圧)も大きくなることが期待できる。

つまり同時に多数のフラッシュメモリーセルを加算する構成にすれば、電圧をそれほど上げなくても合計の電流量が増え、結果的に精度をそれほど落とさずに消費電力を抑えられる。

他にも懸念事項がないわけではないが、それは既存の技術で対応が可能である、というのが発表内容であり、今回は省くが、実際に温度との相関やウエイトと精度の相関、消費電力とダイナミックレンジの相関などを実際に示しながら現実的に製品が製造可能であることをアピールしていた。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ