上がらないIPC

さてそのパイプラインに絡む話。記事冒頭の画像でSingle Thread Upliftが15%以上である、と説明された。「たった?」というのが次の議論である。スライドの脚注によれば、これはCineBench R23のシングルスレッドテストでの結果であり、16コアのRyzen 7000の試作品と、Ryzen 9 5950Xを比較しての数字である。

シングルスレッドテストの場合、処理時間がかなりかかるので、インテルにしてもAMDにしてもMax Turbo/Max Boostで動作するのは最初の1分程度であり、すぐにBaseに戻ることになる。ということは、ここでの15%という数字は、Ryzen 9 5950XとRyzen 7000の試作品の、それぞれベースクロックに近いところでの性能比較と考えていいかと思う。

Ryzen 9 5950Xのベースクロックは3.4GHz。Ryzen 7000シリーズはもちろん不明だが、例えば仮にベースクロックが4GHzだとすると、それだけで性能差は17.6%に達する計算である。もちろんIPCが同一、という前提の計算だが、さすがに下がることはあり得ないだろう。

ということは、15%という性能向上のほとんどが動作周波数の向上で占められることになってしまう。この性能向上について、基調講演の20:05あたりからLisa Su CEOは明確に「IPCと動作周波数の向上の両方で実現した」としており、ということはベースクロックはもっと低いことが考えられる。数字で示すと以下のようになる。

| ベースクロックによる性能の向上率 | ||||||

|---|---|---|---|---|---|---|

| ベースクロック | 向上率 | |||||

| 3.5GHz | 2.9% | |||||

| 3.6GHz | 5.9% | |||||

| 3.7GHz | 8.8% | |||||

| 3.8GHz | 11.8% | |||||

| 3.9GHz | 14.7% | |||||

| 4.0GHz | 17.6% | |||||

こうなると、3.6~3.7GHzあたりがベースクロックというのがありそうな感じだ。ということはIPCによる増分は10%に満たない程度になる。

これは逆に言えば、Zen 4のパイプラインは従来同様4命令同時解釈で、発行の方が8命令を9命令にした程度なのかもしれない。5命令解釈、10命令発行だとするとあまりにIPCの上がり方が少ないからだ。

ただこれは別の疑問につながる。だとしたらなぜこんなにダイサイズが巨大なのか? である。5命令解釈/10命令発行なら、それなりにパイプラインの規模が拡大する。この分野で言えばポラックの法則が有名だ。これは性能は回路規模の平方根に比例するというものだ。

今回で言えば、Zen 3を基準にすると、もしZen 4が5命令発行/10命令実行だとすると、IPCはラフに25%向上することが期待できる。その一方で回路規模は56%増大する、というものだ。だからIPCが25%向上するなら、ダイサイズも相応に巨大化することに不思議はない。逆説的に言えば、この程度のIPCでZen 3と変わらないダイサイズはどうしてもつじつまが合わないことになる。

可能性としてあるのは、なんらかの理由でCineBench R23のシングルスレッドテストでは性能が上がり難い(もしくは意図的に動作周波数を低く抑えている)というあたりだろうか。まだ試作品(そもそも基調講演後半の5.5GHz駆動を達成したものと同一のダイかどうかも不明である)だからこのあたりはどうにでもなる。

そこまでして性能を隠す意味があるのか? といわれると困るのだが、他に思いつかないというのが正直なところだ。おそらくZen 4の詳細は出荷直前(9月あたりだろうか?)まで公開されないと思われる(8月のHotChipsは今回はZen3+止まりな気がする)。そこまでの間は、このミスマッチの謎は解けそうにない。

5.5GHz駆動と170WのTDP

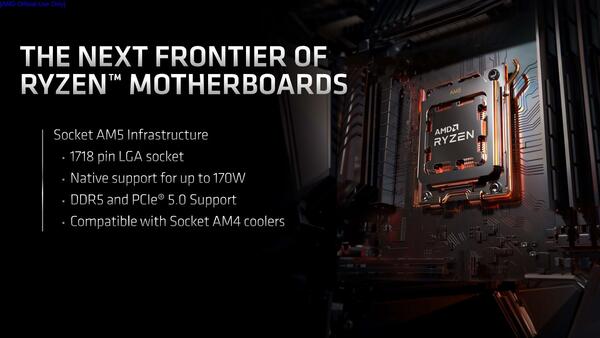

基調講演後半ではGhostwire: Tokyoを実施しながら、ピークで5.5GHz超えを達成しているが、これに先立ってAM5が170Wまでの供給能力を持つことが明らかにされている。

実はこの170Wに関し、Tom's Hardwareが「この170Wという数字は正確でない」というニュースを報じた。この件について筆者もAMDに問い合わせた結果、以下のことが確認された。

Socket AM5では、TDPが170Wまでであるが、それとは別にPPT(Package Power Tracking)が230Wまでサポートされる。PPTはTDP×1.35となっており、なのでTDPが170WのCPUはピークで230Wまで許容されることになる。インテル風に言えばPL1が170W、PL2が230Wとなる形だ。こちらもAlder Lakeに引けを取らない(?)発熱ぶりが期待できてしまうのは、やや残念である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ