6月23日、今年もオンラインでCOMPUTEX TAIPEI 2022が(南港での展示会も同時に開催されているので、オフライン併催という形態ではあるが)開催され、まず基調講演でAMDのLisa Su CEOによりRyzen 7000シリーズが発表になった。すでにKTU氏の記事が掲載されているので、もう御覧になった方も多いと思う。今回はこのRyzen 7000シリーズを少し深堀りしてみたい。

AI向け拡張命令を実装

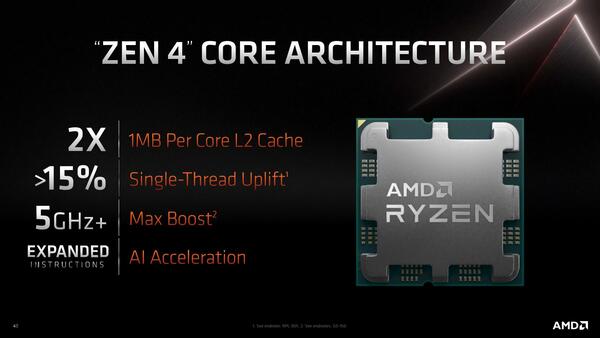

性能の話は後にまわして、まずは下の画像にあるAI Acceleration Instructionsについて。

もともとZen 4世代ではAVX-512命令をサポートする見込み、という話は連載652回でも触れたとおりだ。なので、この延長でAVX-512 VNNIもサポートになったものと筆者は想像している。

もし新たなAI向けアクセラレーターをCPUコアとは別に搭載するならば、別に命令セットはVNNIである必要はない。連載665回で紹介したインテルのGNAのようなパターンだ。

ただこのスライドでも“EXPANDED INSTRUCTIONS”という表記をしているところから、既存のx86というかx64の命令パイプラインの中にAI拡張を施していると考えるのが普通で、となるとアクセラレーター案は現実味が薄い。

ではAI向け拡張を命令パイプラインに統合するとするとどこか? と言えば、一番現実味が高いのはSIMDエンジンである。AIプロセッサーの昨今の一連のシリーズでも紹介してきたように、とにかくAIというかCNN(畳み込みニューラルネットワーク)では、大量のデータを処理するスループット性能が必要になる。現状CPUパイプラインの中でこうした目的で実装されているのはSIMDエンジンであって、逆にSIMDエンジン以外にもう1つ、同じくらいのスループットを持つAIエンジンを持つのは無駄でしかない。

であればSIMDエンジンにAI向けの処理までやらせた方が効率が良い。そしてそのSIMDエンジンがAVX-512対応をするのであれば、VNNIを実装するのは自然な流れだろう。

ちなみにVNNIそのものにはあまり多くの命令は含まれておらず、以下の項目しかない。

- VPDPBUSD(8bit値のMAC演算)

- VPDPBUSDS(VPDPBUSDの符号付き)

- VPDPWSSD(16bit値のMAC演算)

- VPDPWSSDS(VPDPWSSDの符号付き)

したがって、実装はそれほど難しくない(むしろ容易)と思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ