ロードマップでわかる!当世プロセッサー事情 第659回

ISSCC 2022で明らかになったZen 3コアと3D V-Cacheの詳細 AMD CPUロードマップ

2022年03月21日 12時00分更新

3月15日に報じられたように、Ryzen 7 5800X3Dの発売日が4月20日に決まった。それにあわせて、というわけでもないのだがZen 3コアに関する詳細が今年のISSCC(International Solid-State Circuits Conference)で発表になったので説明しよう。

といっても、Zen 3のプロセッサー・パイプラインの話はそれほど新しいものはないので、今回は主に3次キャッシュ周りとトランジスタ構成の話になる。

3次キャッシュの容量が倍になったZen 3

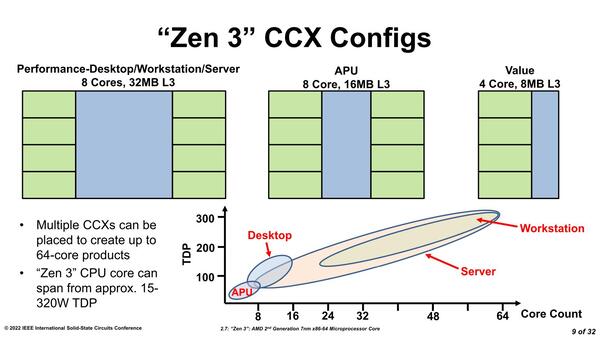

まずCCXのバリエーションについて。Zen 3では実は3種類の構成が当初から想定されていたそうだ。

画像の左がいわゆるMatisseの構成であり、Ryzen 5000シリーズとEPYCがこれを利用しており、中央は(厳密に言えばZen 3+ベースになったが)Rembrandtコアで、Ryzen 5000GシリーズやRyzen 6000Gシリーズとして流通している。

一番右はバリュー向けだが、現在AMDはここにZen 2ベースのRyzen 4000シリーズ/Ryzen 4000GシリーズやAthlon 3000シリーズを充てており、おそらくこの先も4コア/8MB L3のZen 3ベース製品は登場せずに終わることになるだろう。

もっともこれは技術的というよりはマーケティング的な要素で決まる話であり、少なくともZen 3の設計段階においてはそこまで読み切れなかったので、4コア/8MB L3のCCX構成を作ることも可能な構成にしていた、ということになる。要するにCCXは8コアのみでなく、4コアの派生型を作ることも可能だったというのはおもしろい。

そしてL3は、32MBは当初からTSVが想定され、一方APU用の16MBはTSVなしとしてデザインされており、これとコアを組み合わせるモジュラー設計になっているとされた。

TechInsightの解析で、現在販売中のMatisseにもTSVの準備が行なわれていることがわかっており、つまりZen 3コアの開発時点からTSV付きになることは想定済みだったわけだが、このスライドでもそれが再確認できたことになる

さてL3の構成であるが、内部は32B/サイクルの帯域を持つリングバスがデュアル構成になっているということが今回明らかにされた。

このあたりはインテルのCoreシリーズにも通用する話だが、やはりこうしたケースで大規模なファブリックを入れるよりはリングバスの方が効率が良いということだろう。ただCoreシリーズは基本シングルリング(ただしリングストップがダブル)なのに対し、双方向のデュアルリングというのはXeon Scalableに近い。このあたりはRyzenだけでなくEPYCに使うことも想定していることの裏返しかもしれない。

利用しているセルライブラリーが、HC(High Current)からHD(High Density)になっているのも興味深い。HCはZen 2世代で使われていた、高速向けのセルライブラリーだ。これに対してHDは密度重視、つまり速度よりもトランジスタ密度や省電力を重視したライブラリーとなる。Zen 2→Zen 3でL3容量が倍になったことが理由と思われるが、これにより面積を14%削減、消費電力24%削減というのはバカにならない。

このリングバス(とリングストップ)の詳細が下の画像だ。Zen 3の場合、L3は16-way Set Associativity(これはMatisseだけでなく、Rembrandtも同じ)であり、これを8スライスで分割するのでスライスあたり2-wayの構成になっているのだが、そのスライスごとにこのリングストップが入っている格好だ。

SW0/RPT0とSW1/RPT1はそれぞれのリングバス用のスイッチとリピーターであるが、このSW0/SW1は左でわかるように、横方向の接続に向けた構成になっている。だから技術的にはリングではなくメッシュ構成にすることも可能だと思うのだが、多分そこまでしても性能向上がそれほど望めなかったのだろう(このあたりの詳細は講演でも語られなかった)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ