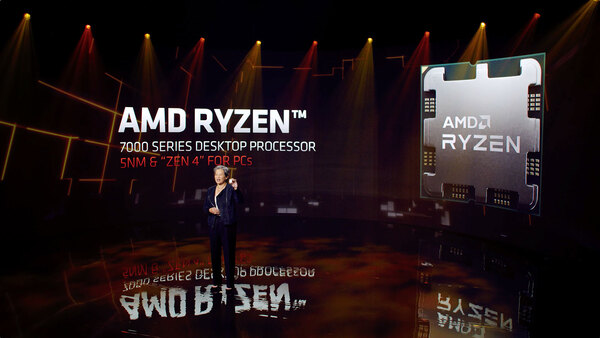

前回はZen 3/Zen 3+ベースの2製品を説明したので、今回はZen 4ベースの話である。といってもKTU氏のレポートでもわかるように、実はあまり情報がない。現状で言えば、以下がAMDからの公式な情報である。

- 新Ryzenは7000シリーズの型番になる。製造プロセスは5nm。

- 新ヒートスプレッダは開口部の多い独自方式。

- パッケージはついにPGAからLGAに変更、Pad数は1718になり、DDR5/PCIe Gen5に対応。CPUクーラーの形状はSocket AM4と共通。

- 出荷は今年後半で、CPUとプラットフォームが同時提供。

RembrandtがRyzen 6000シリーズ、RaphaelことZen 4 RyzenがRyzen 7000シリーズになったわけだが、さてRebmbradt後継となるPhoenix(Zen 4ベースのGPU統合モノシリック)はRyzen 7000シリーズなのか、Ryzen 8000シリーズなのか、どっちなのだろう?

※お詫びと訂正:記事初出時、「パッケージはBGAからLGAに変更」とありましたが正しくは「パッケージはPGAからLGAに変更」になります。記事を訂正してお詫びします。

Socket AM4とAM5でヒートシンクは共通

ヒートスプレッダの大きさはほぼ変わらない

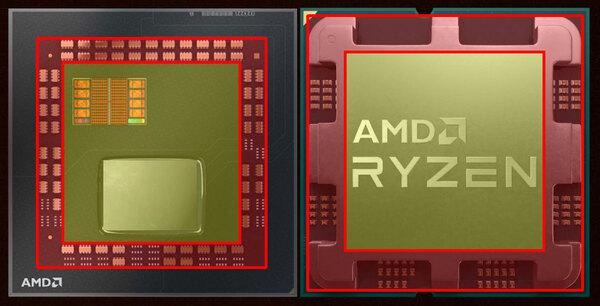

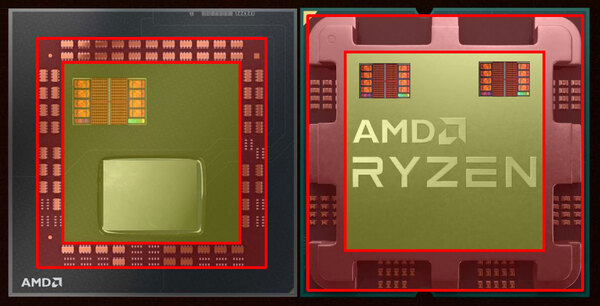

ではここから深堀りしていきたい。まずヒートシンクについて。下の画像は、Ryzen 7 5800X3DとZen 4 Ryzenの両方が掲載されたスライドから抜粋して、縮尺を調整したうえでいろいろ細工したものだ。

そもそもSocket AM4とAM5でヒートシンクが共通、ということはパッケージのサイズは大きくは変わらないものと考えられる。Socket AM4の場合、ピンは39×39列で1521ピン分実装可能だが、中央に余白があるので1331ピンとなっている。

ただピンよりLGAのPadの方が実装密度を上げられるし、実際インテルもLGA1700をほぼ同じ大きさで実装している(多少縦長だが)。実際にはAM5の方が微妙にパッケージは大きくなる可能性があるが、その場合でも同じヒートシンクを使えるという時点でヒートスプレッダの大きさは大きくは変わらないと見られる。せいぜいが現在の39mm角が40~41mmになる程度だろう。

一応ここではパッケージのサイズが変わらないという前提で話をすると、ではヒートスプレッダが穴付きになった理由は? といえばパスコンの位置がより外側に配されるようになり、これを避けるために空隙を作らざるを得らなかったのだろう。

これは上の画像を見比べるとわかるが、パスコンを置くエリア(赤線で囲われた部分)がパッケージの外縁により近いところに配されていることがわかる。この結果、CCDとIODを配置できる部分(黄色)がより大きくなった形になる。

ではなんのためにこのような変更をしたのであろうか? 普通に考えれば、ダイサイズが大型化した、というあたりが予測できるのだが、そもそも製造プロセスをTSMCのN7からN5に変更したことで、ダイそのものは相当小型化されると予測される。なにしろTSMCの説明ではこのN7→N5で以下の利点が見込めるとしている。

- エリアサイズを45%縮小

- 同一動作周波数なら消費電力20%削減

- 同一消費電力なら動作周波数15%向上

現在のZen 3コアがおおよそ72mm2と推定されるので、これをそのままN5に移行すると40mm2程度まで縮小できる計算になる。下の画像はZen 4 Ryzenのパッケージの上に、45%縮小したZen 3のダイを2つ載せた図であるが、明らかに余白が多いというか、そもそも黄色いエリアをわざわざ大きくした理由がわからないほどにスペースが余る計算になる。

実際にはZen 3→Zen 4ではかなりパイプライン構造を増やすと思われるし、3次キャッシュの容量も増やすだろうが、それでもせいぜいが50mm2程度に収まるだろう。特に3次キャッシュに関しては3D V-Cacheを利用する可能性もあるわけで、すると3次キャッシュの容量を増やしてもダイサイズは増えないことになる。

3D V-Cacheの方式にすると、下位モデル(Athlon、Ryzen 3/5)は3次キャッシュを少なめ、上位モデル(Ryzen 7/9、EPYC)は多めにするといった作り分けが容易になるので、例えばダイそのものの3次キャッシュ容量は現在と同じ32MBのままにして、上位モデルはそこに32MBなり64MBを積層する形で性能とコストの差別化を図りやすくなる。それを考えると、ダイサイズはやはり大きくても50mm2程度と想像する。

ではIODが大型化するのか? というと、おそらくそれもノーである。実はZen 4世代からはついにすべてのSKUで原則GPUが統合されるらしい(インテルで言うところのF SKUに相当するものが用意されるかどうかは不明)。これはIODの側に統合される格好だ。

このIODであるが、TSMCのN6で製造という話になっている。構成であるが、メモリーコントローラーとPCIeのコントローラー、いわゆるチップセット機能(電源管理やI/O、ブート、セキュリティー)に加えて、2CU構成のRDNA2が搭載されるとしている。そして肝心なのは、製造プロセスがTSMCのN6になると言われていることだ。

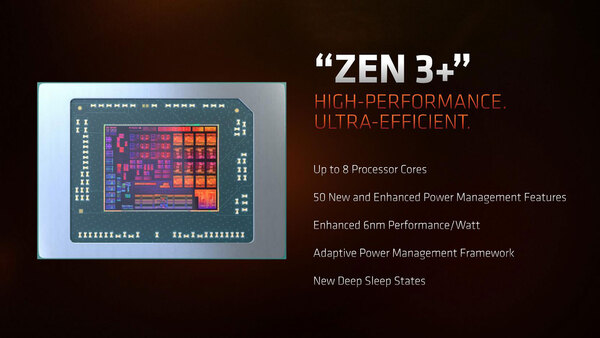

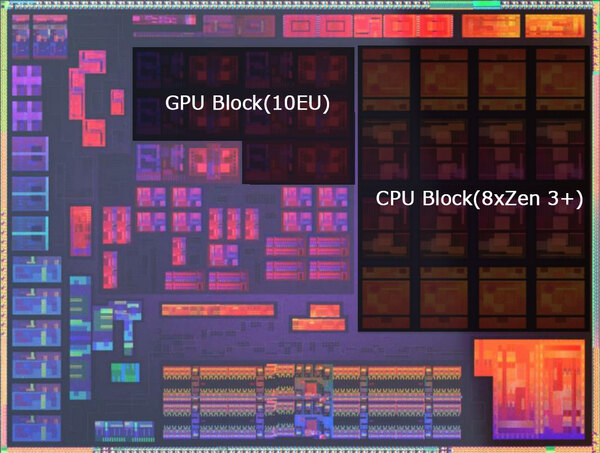

AMDはすでにTSMCのN6を使い、Navi 24ことRadeon RX 6400/6500XTと、Ryzen 6000 Mobileシリーズを製造している。そのRyzen 6000 Mobileのダイは下の画像に示された通りである。

実はこのRyzen 6000 MobileのダイからCPUを取り去り、CUを2つに減らしたうえで、CCD接続用のインフィニティー・ファブリックのI/F(というかPHY)を追加すれば、IODが完成する。

下の画像は先のスライドからダイ部分を拡大して抜き出したものだ。ブラックアウトしている部分が、Ryzen 6000 Mobileにあって、IODには不要な部分である。CPUコアは全部要らないし、CUも12CU→2CUに減らせるので大幅にエリアサイズを削減できる。

今のところRyzen 6000 Mobileシリーズのダイサイズは不明なのだが、FP7と呼ばれる全体のパッケージサイズは35×25mmと言われており、これが事実だとすればダイサイズは16.2×12.3mmで199.3mm2ほどとなる。

面倒なので200mm2として扱うが、上の画像でブラックアウトした面積は全体の37.6%ほど。つまりブラックアウトした部分を除いた、Zen 4向けIODに必要と思われる部分の面積は62.4%の124.8mm2となる計算だ。

この数字は、現在のZen 2/Zen 3ベースのRyzenで使われているIODのサイズ(125mm2)とほとんど変わらない計算になる。実際にはここにインフィニティー・ファブリックのPHYの追加があり、内部の再配置にともない多少無駄が増える可能性はあるが、その一方でSATAなどのI/Oやブートなどの機能は外付けのチップセット側でまかなえるので、その分の面積が減る(減らない可能性もある)。

したがって、おそらく130mm2程度まで大型化する可能性はあるが、140mm2まで行くことはないだろうと思われる。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ