Bergamoの構成を推定

1CCXあたり8コアでトータル128コアか?

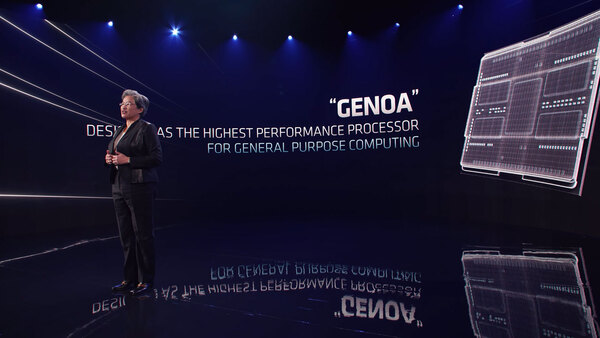

ところでプラットフォームの話だが、Genoaのパッケージ内部のCGを見る限り、12個のCCD+1個のIODという、Milan世代の基本構成は変わっていないように思える。

まだこのMilan世代のパッケージサイズなどは明らかになっていないが、現行のEPYCと大きく変わらないと考えると、ダイ1つあたりの大きさはやや小さくなっているようだ。

さて問題はBergamoの構成である。おそらくIODはGenoaと共通であろう。なので可能性としては以下の2つのパターンが考えられる。

- 1個のダイに16コアのBergamoが搭載され、これが合計8ダイで128コア

- 1個のダイに8コアのBergamoが搭載され、これが16ダイで128コア

ちなみに1つ目の場合、CCXを16コアまで増やすのか、それともCCXは8コアのまま、2つのCCXを1つのCCDに搭載するのか、という2通りの可能性があるのだが、筆者としてはダイあたり2CCX、1CCXあたり8コアという案を推したいところだ。

さすがに16ダイの搭載は実装コスト的にどうよ? という話ではあるし、そもそもTSMCのN7→N5でトランジスタ密度を倍増できるなら、高密度ライブラリーを使う前提なら、Zen 4cの16コアCCDはZen 3の8コアCCDと同程度のダイサイズに収まるだろう。

ダイとパッケージをつなぐインターコネクトのball(ダイ底面に配される、配線接続用のBGA Ball)の数を確保するためには、あまりダイサイズが小さいのは不利になる。もちろんZen 4cを他の用途(例えばデスクトップ向け)に転用するつもりなら、CCDあたり8コアに留めておく方が有利だろうが、今のところそうした計画が一切聞こえてこないあたりは、CCDあたり16コアでもかまわないように思う。

そしてCCXを1つにするか2つにするかだが、CCXあたり16コアまで拡張すると、おそらく論理設計側にも手を入れる必要があるだろう。もちろんZen 4cが「全く」論理設計に手を入れないか? というとそれはそれで難しいので若干は入るだろうが、CCXの構成そのものは少なくともZen 4/4c世代では手を入れないだろうと筆者は推定している。

以上のことからBergamoは8CCD、1CCDあたり2CCX、1CCXあたり8コアでトータル128コア、という案を提示しておきたい。このBergamo、2023年前半に市場投入とされている。物理設計に1年くらいかかるという昨今のCPUデザインの事情を考えれば、Genoaから1年遅れというスケジュールは非常に納得できるものである。

ちなみにエリアサイズがZen 4とZen 4cでは大きく変わらない(せいぜい4分の3程度)という予測が前提なので、デスクトップにZen 4cは来ないと筆者は予測している。big.LITTLEへの対応ができていないわけではない(*2)が、Armにしてもインテルにしても、bigコアとLITTLEコアの大きさが大きく異なっており、LITTLEコアはbigコアの数分の1(*3)まで縮めないとbig.LITTLEのメリットは生まれにくいように思う。

その見方でいけば、現在のZen 4cは大きすぎるように思う。ちなみに次で触れるが、Zen 4とZen 4c(というよりGenoaとBergamo)ではややSIMD命令周りに差があるかもしれない。

(*2) 例えば2019年12月にAMDは“Method of Task Transition Between Heterogenous Processors”という特許を出願し、2021年に登録されている。

(*3) Alder Lakeで見る限り、E-CoreはP-Coreの4分の1くらいのエリアサイズに見える。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ