AMDが米国時間の11月8日に開催したオンラインイベント“AMD Accelerated Data Center Premiere”の概略は発表記事にまとまっているが、これをもう少しかみ砕いて説明していこう。まず今回はMilan-Xの話である。

AMDがMilan-Xこと第3世代EPYCを発表

2022年第1四半期に投入

今回の発表内容は「3D V-Cacheを搭載したMilanベースのEPYCを、2022年第1四半期に市場投入する」の一言に尽きる。この3D V-Cache搭載MilanはMilan-Xというコード名なので、以下記事内でもMilan-Xで通すが、このMilan-Xはすでに特定顧客への納入が始まっていることも明言されている。

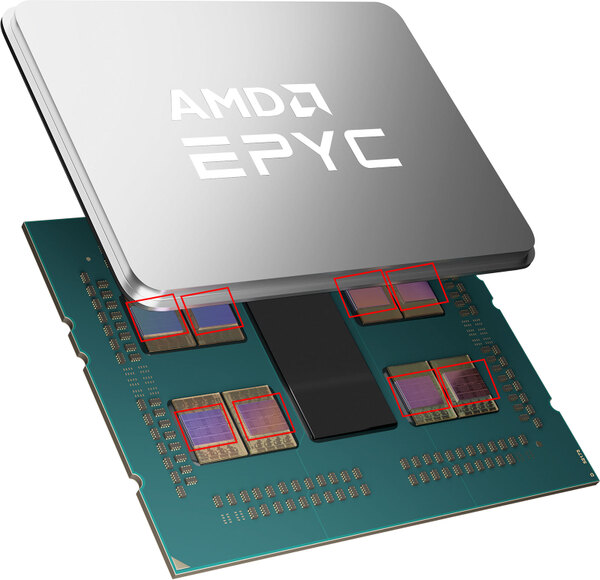

さて、そのMilan-Xであるが、こちらは純粋にMilanの既存の8つのダイを、3D V-Cache付きに更新しただけである。

キャッシュは以下のとおり。

- L1:(命令32KB+データ32KB)×8=512KB

- L2:Unified 512KB×8=4MB

- L3:Unified 32MB→Unified 96MB

ダイあたりで言えば合計100.5MBとなり、EPYCは最大8ダイなので100.5MB×8=804MBとなる計算である。

下の画像の3Xは、L3が32MB→96MBになるから3Xという話で、その意味では下の画像にあまり新しい話はない。

3D V-Cacheそのものは連載618回で技術的な要素を説明しているので今回は特に触れない。3D V-Cacheには以下の特性があるので、Milan-Xの動作周波数やTDPなどは、おそらく現行のEPYC 7003シリーズとほぼ変わらないものになるだろう。

- レイテンシーは3D V-Cacheの有無でそれほど大きな差はない(微妙に大きくなる)

- 消費電力も3D V-Cacheの有無でそれほど大きな差はない

- コアの動作周波数そのものには影響がない(内蔵L3と同じ動作周波数で動くため)

ちなみにレイテンシーが微妙に大きくなるというのは、一般論としてキャッシュを増やすと「キャッシュのどこに、どのメモリーアドレスの内容が格納されているか」を記録しているTag RAMのサイズが当然増えることになる。

するとTag RAMの平均的な検索時間が延びることになる。Tag RAMの先頭で目的のアドレスを見つけられれば、Tag RAMのサイズに関係なく最小ですむが、Tag RAMを全部検索して最後で見つけた場合は、Tag RAMのサイズが増えると余分に時間がかかることになるからだ。

もちろんこの検索は最速で行なわれているから、これでレイテンシーが10サイクルも増えたりはしないし、Tag RAMの「どこで」見つけるかにもよるので、必ずレイテンシーが増えるとも限らない。ただ平均的には1~2サイクル程度のレイテンシーの増加が見込まれると思われる。

これによる性能劣化よりも、L3容量を3倍増にしたことによるメモリーアクセス性能改善効果の方が圧倒的に大きいので、おそらく通常のベンチマークではこれによる性能の劣化はまずないだろう。加えて消費電力や動作周波数にはほぼ影響がないため、Milan-Xは純粋に性能が改善したMilanとして扱えるわけだ。

では性能としてはどうか? ということでAMDから示された例が下の画像だ。

16コアのEPYC 73F3では1時間あたり24.4本の検証ジョブを実施できるのに対し、同じ16コアの3D V-Cache搭載EPYCでは40.6本のジョブを実施できたという話で、66%の向上が見られたとしている。

AMDから出された性能評価はこれで終わりだが、まだ公式には製品発表前ということもあるので、おそらく来年のCESあたりでもっと細かな性能評価が出てくるものと思われる。現時点では、いくつかのISVがすでにMilan-XベースのEPYCへの対応を進めていることのみが表明されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ