ロードマップでわかる!当世プロセッサー事情 第623回

Lakefieldが生産終了、Sapphire RapidsはPCIe Gen5とCXL 1.1をサポート インテル CPUロードマップ

2021年07月12日 12時00分更新

Sapphire Rapids追加情報

6月29日にインテルはISC 2021(International Supercomputing Conference)に合わせていくつかの発表を行なった。この中でSapphire Rapidsに関する追加情報が開示された。といってもそれほど多くなく、以下の3つが示されただけである。

- (1)Sapphire Rapidsの中にはHBM2を実装したSKUが含まれる

- (2) PCIe Gen5とCXL 1.1をサポート

- (3)Intel AMXを実装

このうち(3)については連載569回で説明した通り。拡張命令というよりは、アクセラレーター制御命令と呼ぶほうが適切な気がする構成であり、ただSapphire RapidsにはXe GPUは搭載されない「と思う」ので、AMX専用アクセラレーターが別途実装される形になる。

ダイ的にはCPUと同一だろうが、CPUパイプラインの外に、ちょうどSunny CoveにおけるGNAのような形で実装されると筆者は予想する。

(2)の話は順当で、それほど驚きはないので良いとして、(1)の話。Sapphire RapidsのHBM2搭載の話は連載586回で下の構成図を紹介したが、割と真面目にこれに近い構成になりそうな気がしてきた。

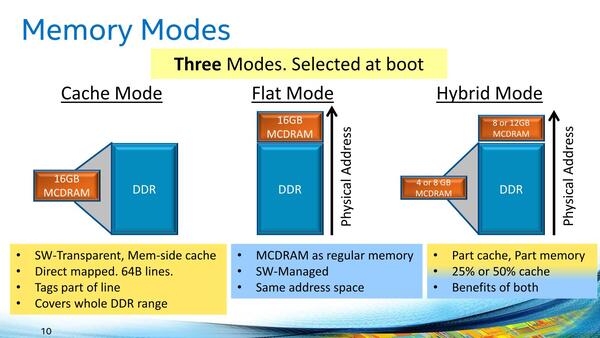

インテルはこのマルチメモリー構成を、かつてKnight Landingで実装した。この時は6ch DDR4+8ch MCDRAMというこれはこれでお化け構成だったわけだが、Knight LandingはこのMCDRAMを、以下の3つの使い方ができるとしていた。

| MCDRAMのモード | ||||||

|---|---|---|---|---|---|---|

| Cache Mode | DDR4メモリーのキャッシュとして使う | |||||

| Flat Mode | MCDRAMもメモリーの一部として扱う | |||||

| Hybrid Mode | MCDRAMの一部をキャッシュに割り当て、残りをメモリーの一部として扱う | |||||

DDR4×6chの帯域は115.2GB/秒(DDR4-2400)で容量は最大384GB、MCDRAMは容量こそ16GBながら理論帯域は1280GB/秒(160GB/sec×8)、実性能で言えばTriadというベンチマークを実行したとき、DDR4が90GB/秒そこそこなのに対し、MCDRAMは400GB/秒超で、ほぼ5倍近かったそうだ。効率(理論値との比)を考えると「?」ではあるが、とにかく高速なDRAMとして使えたわけだ。

インテルはSapphire Rapidsで、どうも同じ仕組みを提供しようとしているように見える。日本語のリリースでは「これにより、プロセッサーが利用できるメモリー帯域幅が劇的に拡張され、メモリー帯域幅の影響を受けやすいHPCアプリケーションの性能が大幅に向上します。ユーザーが、ワークロードで使用できるメモリーは、広帯域メモリーのみ、もしくはDDRと組み合わせた使用が選択できます。」とあって、どう見ても下の画像のような使い方が想定されている気がする。

HBM2ではスタック当たり256GB/秒であったが、2018年に追加策定されたHBM2Eなら307GB/秒まで帯域が広げられている。DDR5は当初DDR5-4800止まりとみられるので、これが2chで76.8GB/秒。つまりHBM2Eを使えば帯域が4倍に広がるわけだ。なんというか、「そりゃ消費電力が400W行くよね」という感じの構成になっている。

ちなみに同時期に投入されると目されるMilan改(Stacked L3 Zen3ベース)の場合、DDR4-3200のサポート止まりの代わりに、パッケージ全体の3次キャッシュは768MBにも達する。しかもレイテンシーそのものはほとんど増えない。さて、どちらの手法が効果的であろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ