11月19日、米EETimesはMythicが初のAIプロセッサー搭載M.2カードをリリースしたことを報じた。このM.2カードに搭載するM1108というプロセッサー(最近同社はAMP:Analog Matrix Processorと称している)、なんと性能は35TOPSである。

連載583回で紹介したQualcommのCloud AI 100の場合、Dual M.2構成のものが50TOPS以上とされているから、(こういう計算が正しいかどうかはともかくとして)M.2 1スロットあたり25TOPS以上ということになり、MythicのM1108はこれを上回る性能を実現していることになる。問題はQualcommのような資金力のある大手ではなく、スタートアップ企業でしかないMythicがこれをどう実現したかという話である。

商業的に成功した例がない

Compute-in-Memory型アーキテクチャー

Mythic, Inc.は2012年にテキサスで創業したスタートアップである。スタートアップと言いつつ直近では100名を超える従業員がいるし、拠点もテキサスだけでなくRedwood Cityにオフィスを構えるまでになっている。

Redwood Cityは、シリコンバレーの北にあたり、かつてはシリコンバレーの「外」扱いされていたが、最近はシリコンバレーの範囲がサンフランシスコあたりまで広がってる関係で、いつの間にかシリコンバレーの中になっている。物理的にはOracleの本社のご近所にあたる。

そのMythicは、Linley Processor Conference Fall 2019において創業者兼CTOのDave Fick氏が“A Graph-Based Dataflow Architecture for Executing Neural Networks”という講演を行なっている。この時に講演した同社のIPU(Intelligence Processing Unit)が、その1年後である今年11月に製品としてリリースされた、というのが冒頭の記事である。シリコンの製造や製品出荷の手前でつまずくスタートアップが少なくないだけに、ここまで来たのは大きな進展である。

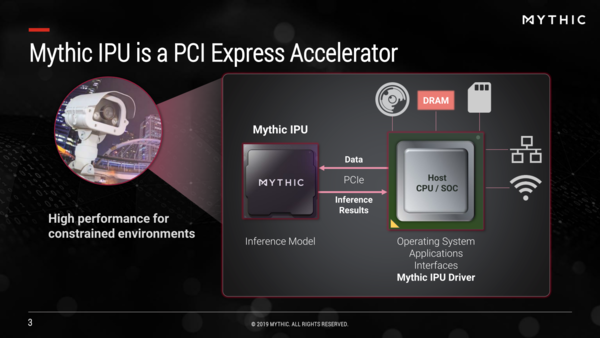

さてそのMythicのIPUであるが、大きな構造は下の画像にあるような形だ。ホストとはPCI Expressで接続され、画像なり何なりの推論元データがホストから送り込まれ、IPUからは推論結果が返ってくるという形だ。

問題はこの中身である。MythicはこのIPUに3つの要素をブチ込んだ。

- Compute-in-Memory

- Dataflow Architecture

- Analog Computing

このうちDataflow Architectureは、連載568回のWave Computingの回で説明したので割愛するとして、残りの2つ。Compute-in-Memoryは、それこそ80年台から出ては消え、出ては消えしているアーキテクチャーである。連載568回の冒頭にもあるが、要するにCPU内部の消費電力を子細に分析すると、例えばFP64の演算であっても、演算そのものに要する電力よりも、演算のためにデータをメモリーなりレジスターなりから演算器にコピーし、結果を書き戻すという「データの移動」に要する電力の方がはるかに大きいという話である。

これは従来型のCPUの構造では、多少改良することはできても大きく削減するのは難しい。ところが、メモリーと演算器を一体化してしまい、「演算は自身のメモリーセルとしかしない」と制約をつけてしまえば、演算に要する消費電力が大幅に削減できるというわけだ。

これがIn-Memory Computingの基本的な考え方である。実際、この構造を利用してメモリーセルに簡単な演算器を組み合わせたDRAMや、メモリーセルに1bitの演算器を組み合わせたMemory Cell Matrix(というよりConnection Machineの親戚というべきか)などが過去に発表されている。

ただこの方式で商業的に成功した例はこれまでない。1つはこの方式は必然的にMassive Parallel Processor(大規模並列処理プロセッサー)ということになるから、逆に演算器1つ1つは、そんなに難しい処理はできないことになる。なので複雑な演算を行なう場合、結局複数セルの演算器を組み合わせて処理することになり、こうなると途端に効率が落ちる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ