また2週ほど空いてしまったが、AIプロセッサーの話に戻ろう。2019年のHotChips 31で一番会場を沸かせたのが連載572回で紹介したCerebras SystemsのWSE(Wafer-Scale Engine)だった、という話はすでに説明した通り。

ちなみに同社、今年のHotChips 32では“The Second Generation Cerebras Wafer Scale Engine”という講演を予定している。まさか7nmに微細化だったらすごいのだが。

さてそのHotChip 31でそのCerebras Systemsの講演を挟んで行なわれた講演が、インテルのSpring Crest(Nervana NNP-T)と、Habana LabsのGOYA/GAUDIであった。講演の際はWSEにやられたという感じでそれほど話題にならなかったが、年末になっていろいろ騒がれ始めたこの両社の製品を、今回は取り上げたい。

インテルがNervana Systemsというスタートアップを買収

欲しかったのはNVIDIAに対抗できるAI向けプロセッサー

2016年8月、インテルはNervana Systemsを買収した。買収金額そのものは未公開だが、近い筋からはおおよそ4億800万ドル程度とされた。

Nervana Systemsは2014年創業のスタートアップで、従業員も48人しかいなかったことを考えると、かなりの大盤振る舞いという気もする。もともと2016年の時点で同社が提供していたのは、Nervana Cloudという機械学習に特化したクラウドサービス、および機械学習に向いたNEONというフレームワーク「だけ」であった。

ただNervanaは“Nervana Engine”と呼ばれるASICを開発中であり、これを利用することでGPU(言うまでもなくNVIDIAのGPUのことだ)よりも高速に推論が可能という話になっていた。

このNervana Engineこそが、インテルの欲しいものであった。まだ2016年当時はAIのブームが始まったばかりという状況であり、NVIDIAを含めて専用チップはほとんど存在していない状況だったので、そうなると数値演算能力の高さでNVIDIAのGPUが特に学習マーケットで大きなシェアを取ったのは半ば必然であった。

ただインテルはそれを指をくわえてみているわけにはいかなかった。もちろんインテルはKnights Hillという、NVIDIAのGPUに十分伍する性能を持つアクセラレーターを開発中ではあったが、ここにはKnights Millとして2017年に投入されたAVX512のDL拡張機能は含まれない予定だった。

となるとKnights Hillが予定通り出ても、単にNVIDIAのGPUと互角という話であって、マーケットシェアをひっくり返すには十分ではない。それもあって、Nervana Engineが魅力的に映ったのだろう。

そしてそのKnights Hillが2017年にキャンセルされる事態になって、いよいよNervana Engineの投入が急がれたわけだ。

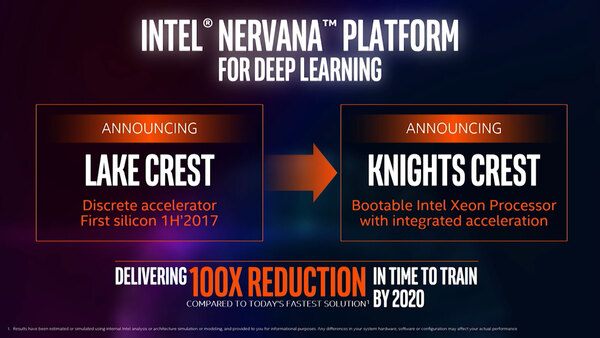

ちなみに最初のNervana EngineはLake Crestの名前で2017年前半に投入され、次にXeonとこのNervana Engineを組み合わせた形のKnights Crestが2018年に投入予定、というのが2016年におけるインテルのロードマップだった。

さて最初のLake Crestであるが、これは12個のTensor Processing Coreに32GBのHBM2、それと12chのICL(Inter-Chip Link)から構成されるものだった。

さらにICLをつかい、3次元トーラス構造で接続数を増やすことで性能をスケーラブルに増強できるとしていた。

ただこのLake CrestはTSMCの28nmプロセスで製造されたもので、それもあってTensor Processing Coreの数は十分とは言えないし、コアの動作周波数もそれほど高くはなかったようだ。

またこの頃には、先に少し触れたKnights Hillがおそらくキャンセルになることが見えていたようで、それもあって(Knights Hillをベースとする予定だった)Knights Crestはキャンセル。Lake Crestは開発用プラットフォームとして配布するにとどめ、商用向けにはTSMCの16nmで作り直したLake Crestの後継となるSpring Crestを提供することを2018年に発表した。HotChipsでの発表は、まさしくこの商用向けのSpring Crestのお披露目だったわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ