HPE(Hewlett-Packard Enterprise)はItaniumベースの製品を(表立ってはできないから、ひっそりと)x86ベースに移行を促す努力をしながら、競合(Dell EMCやLenovo)とのサーバーマーケットのシェア争いを繰り広げていたわけであるが、そのかたわらでおもしろい研究をしていた。それが、The Machineである。

CPUではなくメモリーを中心に設計された

サーバー「The Machine」

The Machineとは、2000年代前半から開発が始まった、非常に意欲的な未来のサーバーである。一口で言えばメモリー主導型コンピューティング(MDC:Memory Driven Computing)を実装するプロトタイプの名前が“The Machine”である。

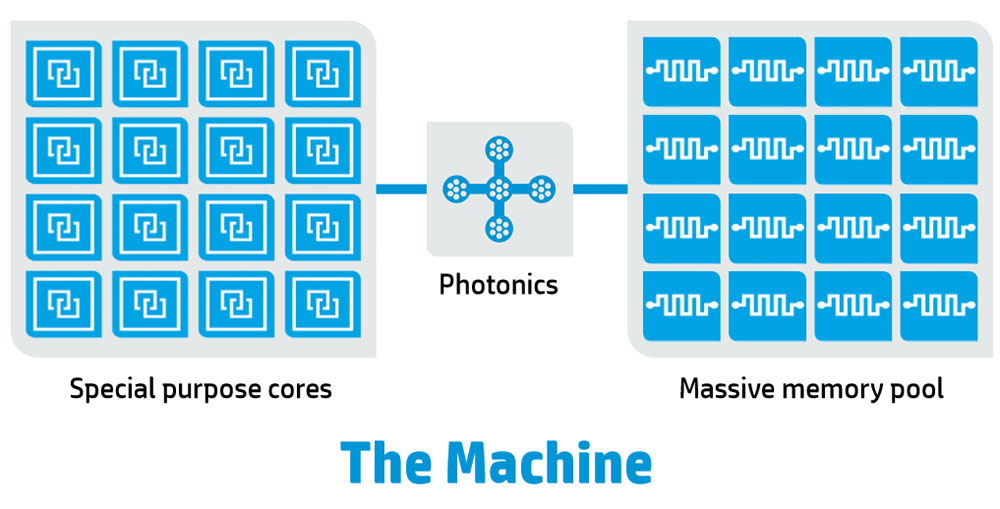

そもそもMDCとはなに? という話であるが、The Machineのコンセプトではメモリーとプロセッサーを切り離すことにある。

通常、メモリーはプロセッサーに接続されており、例えばあるデータをプロセッサーAで処理し、その結果をプロセッサーBでまた処理するといった場合、まずAのローカルメモリーからデータを取り出して処理、その結果をBに送り再び処理し、それをBのローカルメモリーに格納する(だいぶ端折っているのはご容赦を)といった具合に、プロセッサーによる計算(Computation)が主役であり、データはプロセッサーに従属する形でシステムのあちこちに移動することになる。

もちろん昨今のマルチコアの場合は、1つのCPUの中に複数のプロセッサーコアが内蔵されており、共通のメモリーを利用しているため、その範囲で言えば同じメモリー領域を使うことになるが、それこそスケールアウトタイプのサーバーの場合はノードあたりのコア数は控えめに抑える方向にあるので、冒頭に述べたようなシチュエーションは実際にあり得るし、しかもその際には相対的に低速なネットワーク(イーサネットなりなんなり)を経由することになるから、レイテンシーも大きい。

そこで逆転の発想で、メモリーは一ヵ所に集めて、そこに多数のプロセッサーがアクセスする、という構成を取ったのがMCDである。

データの置き場所は移動せずに、プロセッサーが必要な時にそのデータを取り出し、また元の場所に格納する仕組みを取っている。

特徴的なのは、このメモリーは不揮発性であることを前提にしていることだ。つまりメモリーがそのままストレージとしても機能するわけで、これにより処理のたびに遅いストレージから読みだして、処理後に再び遅いストレージに書き戻す手間が必要なくなる。

当然ながらこれはアーキテクチャー的に従来の計算主導型コンピューティング(CDC:Computation Driven Computing)とはまったく異なるため、ソフトウェアレベルでの互換性はなく、MDCにあわせて作り変える必要がある。

ただ逆に言えば、従来はソフトウェア互換性などの理由でx86(もうここではさすがにItaniumという言葉は出なかった)を選ばざるを得ないケースが多かったわけだが、MDCでは別にx86である必要すらなく、さらに言えばCPUである必要もない。GPUとかFPGA、今ならAIプロセッサーなどもここに含まれるが、こうしたもののハイブリッド構成で全然構わないということになる。

ただ、この方式の欠点はプロセッサーとメモリーの間の距離が長くなり、レイテンシーが増えて帯域が減ることである。

そもそもなぜこれまでメモリーがプロセッサーのそばに置かれていたかと言えば、プロセッサーが高速で動くためにはメモリーに高速にアクセスできないと、メモリーアクセス待ちが大量に発生してしまい、性能が頭打ちになるためである。

もう1つ、副次的な理由を挙げるとすれば、広く使われているSDRAM(DDR/DDR2/DDR3/DDR4含む)はいずれも64bit幅(ECCを含めると72bit幅)のパラレルバスであり、物理的にけっこうな配線面積を取る。

したがって、あまり長距離を引き回すと基板への実装が難しくなり、レイテンシーも加速度的に増える。信号線は等長配線が要求されるので、一番配線長が長いルートに合わせて配線の引き回しが行なわれるからだ。結果、無駄に配線が長くなる。

このあたりを嫌って、例えばFB-DIMMやRambusのRDRAM/XDR/XDR2といったソリューションも出てきたものの、ほとんど定着せずに消えていった(XDR2に至っては採用例がないまま終わった)ことを考えると、非標準的なメモリーを利用するのはリスクが高く、するとSDRAMをベースに考えざるを得ず、結果としてプロセッサーのそばに置くしかない、という結果に落ち着くことになる。

これに対するHPEの解は、Silicon Photonicsを利用した光インターコネクトを利用することだった。Silicon Photonicsに関してはいろいろ話がある。この分野、インテルはもう10年以上も研究しているものの、商品化されたのはほんのごく一部でしかなく、現時点でもまだ商用利用が可能なレベルに達しているとは言えない。このインテルの苦闘の歴史は、それだけで1本分の記事以上のボリュームがある。

最近では(NVIDIAに買収される予定の)Mellanoxが一時期ずいぶん関連企業を買収して精力的に開発を進めてきたものの、2018年1月に断念。チームも解散しているといった具合に、実は非常に敷居が高い。

もっともThe Machineのコンセプトが発表された時点では、まだわりと現実的に実現可能と思われていた技術であり、HPEの見通しの甘さを責めるのは難しいだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ