キャッシュと帯域を増やすことで

処理の高速化を実現

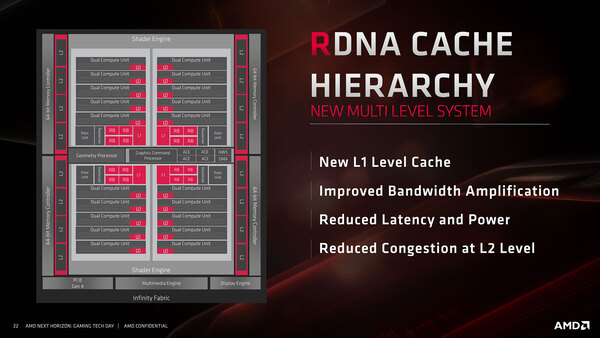

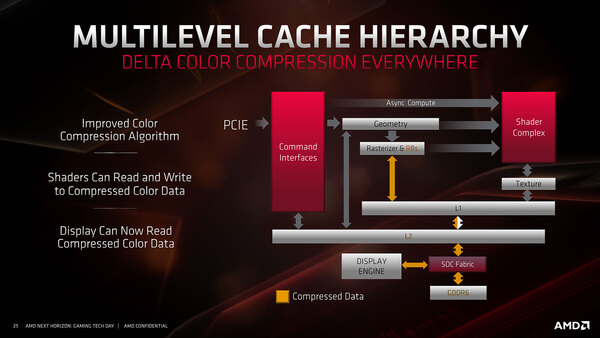

次がキャッシュシステムである。新たに1次キャッシュが追加されたほか、帯域の強化やレイテンシーの削除などが主な改良点である。

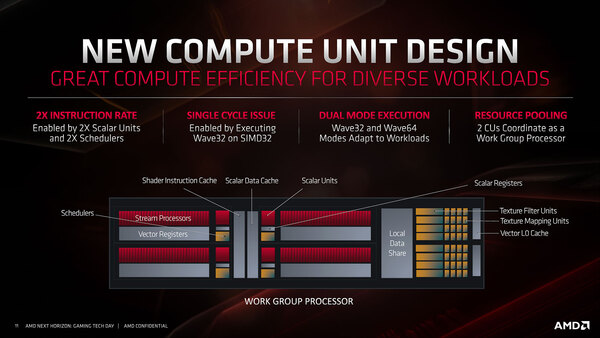

まずキャッシュの説明の前にWGP(Work Group Processor)について定義しておく。先ほどのCUの構成であるが、RDNAでは2つのCUで共有される形でシェーダーの命令キャッシュやScalar Data Cache/Local Data Shareなどが用意される。このCU×2+共有キャッシュの塊がWGPと定義される。

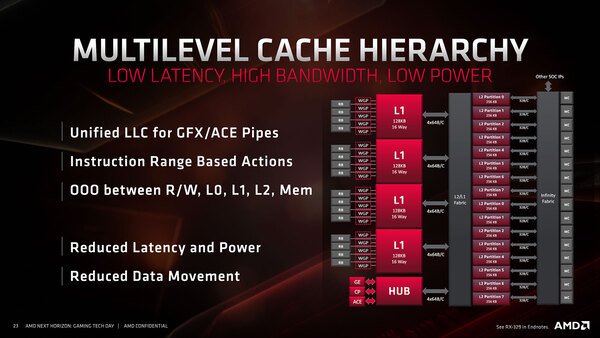

これを念頭に、1次キャッシュの構成を示したのが下の画像である。1次キャッシュには5つのWGP(=10CU)と、RB(Render Backend)が直接接続されることになっている。

実は1次キャッシュの目的は、このRBをフルに生かすための工夫ともいえる。レンダーバックエンドは描画処理の最終段階の作業を担うもので、複数のスレッドをブン回して得られた最終的な描画データを、フレームバッファにピクセル単位で出力する作業を担うことになる。

普通であれば、RBはそのまま2次キャッシュ経由でメモリーに書き出すのが効率が良いわけだが、あえてここに1次キャッシュを挟んだ理由は、Deferred Rendering(遅延レンダリング)の技法が多用されるようになってきたことに起因する。

たとえばLightingを例に取れば、従来型のレンダリング(Forward Rendering)ではオブジェクトに対してLightingの計算を行ない、その結果をラスタライズして出力を得るのに対し、Deferred Renderingでは先にラスタライズを済ませてしまい、その後でラスタライズしたデータに対して必要な箇所だけLightingを施す、という手順になる。

この方式はシェーダーの負荷が軽くなるというメリットがある半面、いったんメモリーに書き出したデータを読み出して処理し、改めて書き戻すことになるので、メモリー帯域に大きな負荷がかかる。

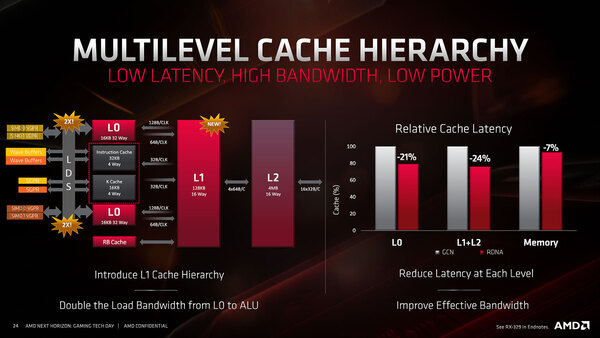

GCNの場合はいったんラスタライズされたデータが2次キャッシュに格納され、RBは2次キャッシュから読み出して処理し、2次キャッシュに書き戻しをし……、という形で煩雑に2次キャッシュアクセスが発生していたが、メモリーより高速とは言え2次キャッシュもそれほど高速ではない。

そこでRDNAではWGP/RBと2次キャッシュの間に1次キャッシュを挟み、RBは1次キャッシュとの間で読み出し/書き戻しを行わせることで処理の高速化を実現した形になる。

それだけでなく、1次キャッシュは0次キャッシュとも広帯域で接続することで、LDS(Local Data Share)の帯域を従来比2倍に増やしたとしており、RB関連以外の処理の高速化にも貢献している。

また、RB⇔1次キャッシュ⇔2次キャッシュ⇔メモリーのデータ転送に関してはデータ圧縮をかけており、これにより効率的に帯域を利用できるとする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ