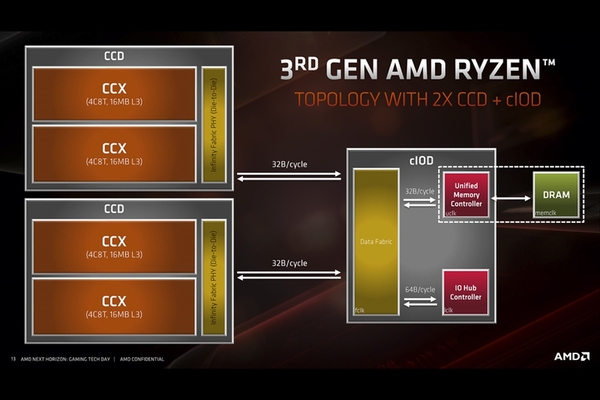

チップレット・アーキテクチャを採用することで

2つの8コアのCCDで16コアCPUを実現

第3世代Ryzenがこうしたシングルソケットで16コアというCPUを実現した背景には、AMDが「チップレット・アーキテクチャ」と呼んでいる新しいCPUサブ基板上に、CPUダイ(CCD)とI/Oダイ(cIOD)を実装していることにある。16コアの3950Xでは2つのCCDと1つのcIODがCPUサブストレート(12層基板)上に実装されている。

従来CPUにあったメモリコントローラやI/Oコントローラ(PCIe、USBなど)はcIOD上に移動しており、CPUにはCPUとInfinity Fabricと呼ばれるCPU-CPU、CPU-I/Oダイを接続するインターコネクトだけが残されている。

CPUとcIODはそれぞれ別のプロセスルールで製造されており(CPUは7nm、cIODは14nm)、製造効率も良く、別々に製造することで歩留まりも向上しているため、製造コストも下がることになる(その分パッケージのコストはあがることになるが、それでもメリットの方が大きいので全体としての製造コストは低下する)。

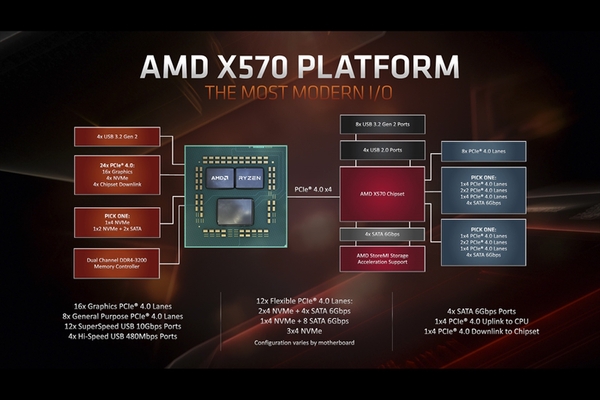

ユニークなのは、AMDはこのcIODのダイを、そのままX570チップセットとして利用している点だ。製造効率もよくなることはもちろんだし、PCI Express Gen 4サポートなど高性能な特徴を、チップセットでも活用できることがメリットとなる。PCI Express Gen 4ではレーンあたり/片方向の転送速度が16GT/秒となり、従来のPCI Express Gen 3の8GT/秒に比べて倍になっている。第3世代Ryzen+プラットフォーム全体で40レーンのPCI Express Gen 4をサポートすることが可能になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります