Ryzenシリーズの最終回は、3月8日に発表されたNaplesの話をしたい。既報の通り、AMDはNaplesと呼ばれる32コアのサーバー向けCPUの存在を明らかにした。

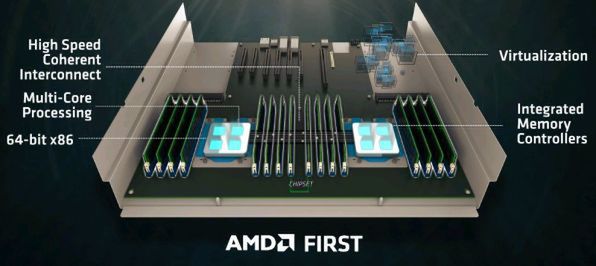

ちなみに、既報の2枚目のスライドは、Naplesのものではない。これは、かつてOpteronでAMDがサーバー市場に参入した際に、64bit(SledgeHammer)も、Native Multicore(Demmark/Italy/Egypt)も、High Speed Coherent Interconnect(HyperTransport Link)も、メモリーコントローラー統合(SledgeHammer)も、Virtualization(Pacifica:後のAMD-V)も、「全部AMDが先鞭をつけた」ことを紹介しているスライドでしかない。

AMDの次世代サーバーCPU

Naples

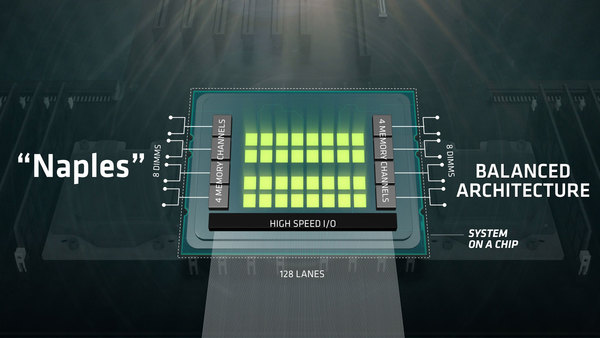

それではNaplesとはなにか? というと、1ソケットで32コア/64スレッドのプロセッサーコアと8ch/16枚のDIMM、さらにPCI Expressを合計128レーン利用可能な構成である。ではこれをどう実現しているかを掘り下げてみよう。

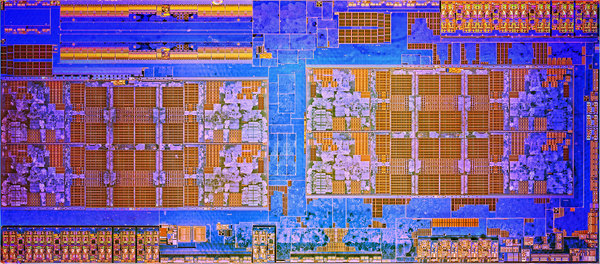

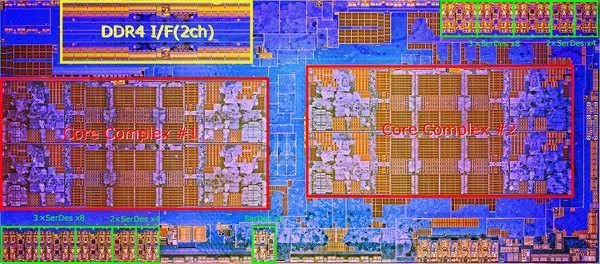

そもそも現在のRyzen 7のダイはどんな構造かをまずは見直してみたい。下の画像はAMDが公開したダイショットであるが、これを機能ブロック別にしたのがさらにその下の画像である。

中央の大きな部分は、4コア+3次キャッシュのコアコンプレックスで、これが2つ存在する。そして左上には、おそらくDDR4のI/Fが2ch分用意されている。

おもしろいのは右上と左下で、これがHigh Speed I/Oのメインとなる部分だが、それぞれ32レーン分搭載されているようだ。ただしSerDesだけでなくコントローラも一緒に入っており、8chのものが3つ、4chのものが2つという構成になっている模様だ。

さて、ここまでAMDはコアコンプレックスの中身やコアの中身については公開してきたが、ダイの内部についてはほとんど紹介してきていない。では実際にどんな感じになっているのか? ということで筆者の想像図が下の画像となる。

筆者が予想するRyzenのダイ構造

実際は周辺回路やAPICなど、まだ欠けている要素はいろいろあるのだが、基本的にはコアコンプレックス2つとメモリーコントローラー、それとPCIe/Infinity Fabric用のSerDes(SERializer/DESerializer:パラレル信号とシリアル信号の双方向変換器)がInfinity Fabricで接続されているという構造になっているのではないかと思われる。

ひょっとするとメモリーコントローラーとコアコンプレックスの間には専用の高速バスが搭載されている可能性があるので、これは黄色の破線で示したが、よほどInfinity Fabricの性能が低いのでない限り、おそらくこの専用バスはなしでいいだろう。

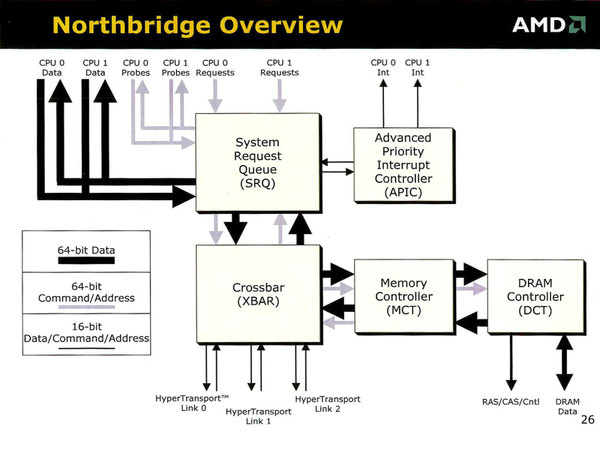

実はこの構造は、K8に非常に良く似ている。K8の世代ではマルチプロセッサーに対応するために、メモリーコントローラーをローカルのCPUコアやキャッシュと切り離して、間をクロスバーでつなぐことで、自身のメモリーアクセスと他のノードからHyperTransport Link経由でやってきたメモリーアクセスを同等に扱える工夫がなされているが、おそらくはRyzenのダイにも同じ工夫があると思われる。

前回の記事でScalable Data FabricがHyperTransport Linkに似ているという話があったが、実際Ryzenのダイ内部もInfinity Fabricでコンポーネントが接続されていると考えると、確かに似ているとするのは理解できる。

Ryzen 7やRyzen 5は、2つのコアコンプレックスとメモリーコントローラー、それとSerDes20レーン分(うち16レーンがGPU用、残り4レーンが300シリーズチップセット接続用)が有効にされて提供されている形であろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ