Ryzenでは電力レギュレーターを内蔵

大容量コンデンサーを利用可能に

次に電力まわりについて。Ryzenではオンチップで電力レギュレーターを搭載した。電力レギュレーターとは、CPUの要求する電圧に合わせて電力を供給するための回路である。従来はこの回路は、CPUの外に置かれていた。この結果、以下のように悠長な処理が必要だった。

- (1) CPUが周波数を変えたいと思う。

- (2) CPUは内部のテーブルを参照して、その周波数に該当する電圧ID(VID)を引っ張り出す。

- (3) CPUからチップセットに対し、VIDを送り出す。

- (4) VIDを受け取ったチップセットは、そのVIDをCPUに電源供給しているPMIC(Power Management IC)に送り出す。

- (5) PMICはVIDを受け取り、これに該当する電圧をテーブルから引っ張り出し、電圧をそれに合わせる。

- (6) 電圧が変化する。

電力レギュレーターを外部に置く理由は、電源まわりはアナログ回路が必須なのでCPU内部に統合できないというものだった。

ただこれだと電圧変更におそろしく時間がかかるので、なんとかCPUパッケージ内に収めることで応答速度の向上と、さらに変換効率の向上を図りたいというニーズが昔からあった。

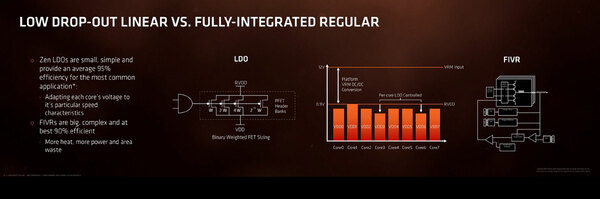

これに対するインテルの回答が、Haswell世代で投入したFIVR(Fully Integrated Voltage Regulator)で、いわゆるスイッチング電源の機能を力技で全部CPUパッケージに載せるものだった。

ただこのFIVRは、逆にCPUの電力レンジがYシリーズの4.5WからSシリーズの91Wまで広がると、1つの回路でカバーしきれないということで廃止になっているなど、なかなかに道のりは遠い。

これに対してのAMDの回答が、LDO(Low Drop Out Regurator)の採用である。LDOとは「入力電圧と出力電圧の差があまりない」もので、端的に言えば抵抗2つで実現できる簡単なものである。

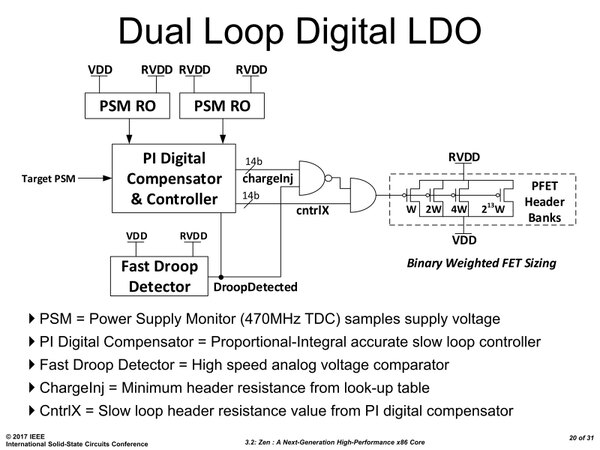

Ryzenの場合、RVDD(これはCPU周辺の電圧レギュレーターから供給される、0.9Vの電源プレーン)から、14個のLDOレギュレーターを順次組み合わせることで、16383通り(0Vは供給するうちに入らないので省く)の電圧をCPUに対して提供できることになる。

この制御と、実際に生成した電圧が望んだものになっているかの監視(Droop Detecotor)もやはりCPU内部に置かれており、非常に短い時間で監視と制御を行なえるようになっている。

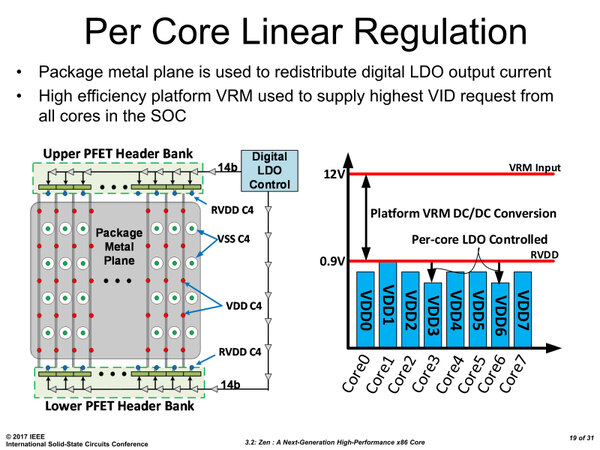

これがどこに入るか? というのが下の画像である。CPUソケット周辺にある電圧レギュレーターは、12V入力を0.9Vに変換、それをRVDDという電力層に供給する。そのRVDDから2ヵ所(図で言うUpperとLower)に、それぞれLDOが搭載されており、ここでコア毎に制御された電圧を供給する、という仕組みだ。

UpperとLowerという2ヵ所に分散して電力を供給するのは、1ヵ所では電圧降下の結果としてLDOのそばは望む電圧が供給されるのに、遠い場所だと低い電圧になってしまう可能性が高いことに対応したからだ。

ちなみに上の画像にはないが、発表会での説明によれば、FIVRは90%程度の効率なのに対し、LDOを利用したRyzenでは効率が95%にも達し、しかもよりコンパクトに収まっているとしている。

ところでLDOであってもFIVRであっても、コンデンサーはなにらかの形で必要になる。Ryzenではヒートスプレッダの内側に隠れているためわからないが、インテルのCPUでは裏面に山ほどバイパスコンデンサー(通称パスコン)が搭載されているのを見た方は多いだろう。

FIVRにしてもLDOにしても、瞬間的な電力変動には追従できないので、これをカバーするためにパスコンが必要なほか、FIVRでは回路構成上コンデンサーがないと面倒である。

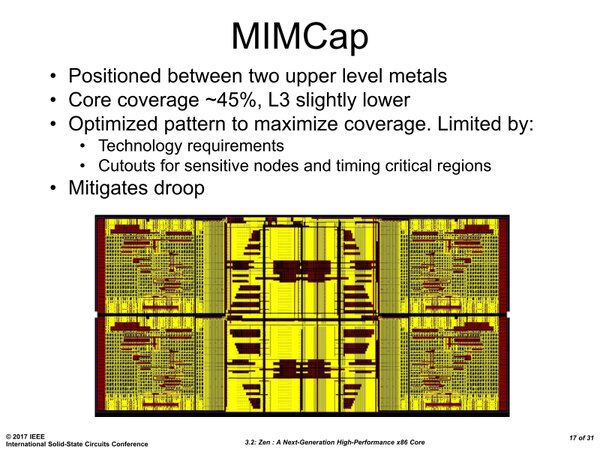

インテルもFIVRを採用した世代ではMiMCAP(Metal-Insulator-Metal CAPacitance)をコンデンサーとして採用したが、Ryzenも全面的にMiMCAPを採用している。

これにより、かなり大きな容量のコンデンサーをダイ上に構築することが可能になっているとされる。今回はこのくらいにして、次回も引き続き、内部構造の話を解説したい。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ