今回のスーパーコンピューターの系譜は、Convex ComputerのCシリーズを解説しよう。

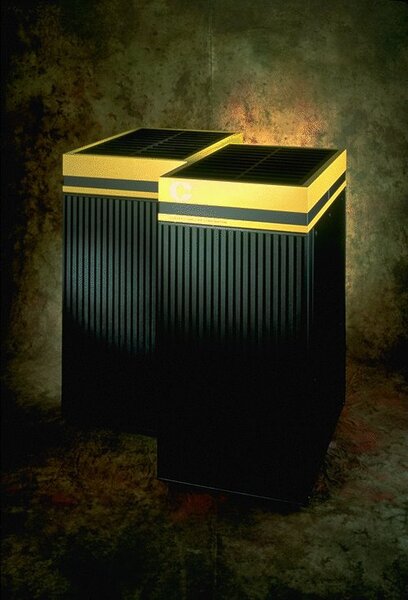

Convex C4600

前回のCydra 5の目的は「手頃な価格で入手できる高機能なコンピューター」である。

1980年代前半というのは、数値演算を利用してさまざまな科学技術計算が行なわれ始めた時期にあたる。この分野におけるCRAYの貢献は間違いなく大きく、これまではできなかったような計算ができるようになったことで、急速に需要を喚起した功績は大きい。

その一方で、CRAYは性能も高かったが価格も高かった。CRAY-1の1号機が納入された価格は連載275回で紹介した通り790万ドルで、さらにストレージが100万ドルである。

1980年代といえば、そろそろCRAY X-MPが市場投入されていた時期だが、CRAY X-MPの価格は構成によってかなり変化するとは言え、絶対的に高価格帯である。 例えば1986年における、SCDへのX-MP/48の納入価格は本体だけで1460万ドル(関連リンク)。1985年におけるベル研究所へのX-MP/24の納入価格は本体だけで1050万ドルとされていた。

これをポンと支払える所は必ずしも多くないわけで、結果として「もう少し性能が低くてもいいから安いマシンを」というニーズが急速に高まっていた時期でもある。

Cydra 5はまさしくこうした市場に向けた製品だったわけだが、そこを狙っていたのはCydromeだけではなかった。ということで今回紹介するのは、やはりこの「CRAYのやや下」の市場を狙ったConvex Computerである。

「CRAYのやや下」の市場を狙った

Convex C1シリーズ

当初はParsecという社名で1982年に創業したが、製品出荷前にConvex Computerと名称を改めている。本社はテキサス州リチャードソンに置かれたが、同じテキサス州でもコンピューター企業が後に集中したオースティンからは300Kmほど離れた場所で、やや珍しい。

創業メンバーはBob Paluck氏とSteve Wallach氏で、Paluck氏がCEO、Wallach氏がCTOの役職を担った。

さて、Cydra 5は低価格でかつ高性能を実現するためにハードウェアアーキテクチャーの側を工夫したわけだが、これに比べるとConvexのアーキテクチャーはそれほど凝ってない。Convexの最初の製品であるCの基本的なアーキテクチャーはCRAYと同様のベクトルである。

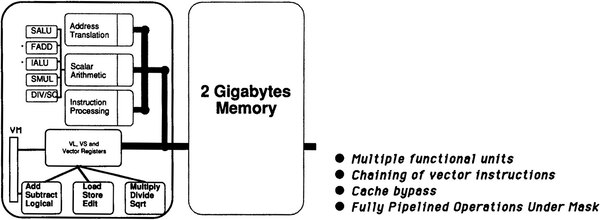

下の画像は、最初の製品であるC1xxシリーズに利用されたC1コアの概略であるが、基本は32bitの仮想アドレスをサポートした、ごく一般的なプロセッサー構成である。

※画像の出典は、"THE CONVEX C240 ARCHITECTURE"。

スカラー演算ユニットは整数演算、アドレス生成、ロードストア、浮動小数点の加算、乗算、除算/平方根と合計6つのパイプラインが別々に用意される。

これとは別にロードストア、加算、乗除/平方根という3つのベクトルパイプラインが用意されており、演算のメインとなるのはこちらである。

このC1コアをベースとした最初の製品であるConvex C120がリリースされたのは1985年のことである。

ちなみに回路はCMOSベースで動作周波数は10MHzとなっており、演算性能は単精度で40MFLOPS、倍精度で20MFLOPSでしかない。

CRAY-1と比べてもかなり低い(CRAY-1は80MHz動作だった)性能ではあるが、CRAY-1と比較すると、例えばVector Registerの数が倍(CRAY-1は64bit×64個のVector Registerが8群だったが、C1は64bit×128個のVector Registerが8群)、メモリーが最大1GB搭載できる(CRAY-1は16MB、CRAY-1Sでも32MBだった)など、性能を落とさない工夫がいろいろ施されており、実効性能で言うとおおむねCRAY-1の5分の1程度、という評価であった。

→次のページヘ続く (高速化しつつ安価に抑えたConvex C2シリーズ)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ