性能が出ればCPUはなんでもいい!

外部の汎用CPU「Alpha EV4」を採用

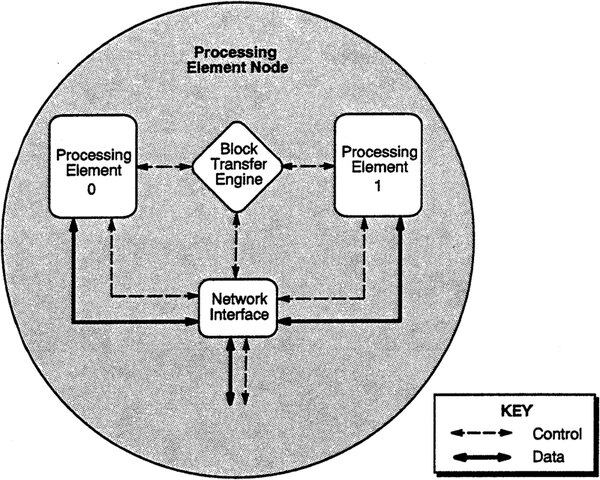

肝心のProcessor Elementであるが、1つのProcessing Element Nodeは2つのProcessing Elementから構成される。

個々のProcessing Elementは、CRIとしては初めて外部の汎用CPUを使うことにした。搭載されたのはDECの150MHz駆動のAlpha EV4こと21064である。

ここでCRIが外部から購入した理由もまた公式には明らかにされていないが、想像はたやすい。というのは、スクラッチから「超並列に向いた」CPUを作るとなると、さらに数年の開発期間がかかる。

CRIはベクトルプロセッサーに関しては豊富な実績とノウハウを持っているが、スカラープロセッサーに関しては(もちろんCRAY-1以来実装はされているものの)それほど知見があるわけはなかった。

さらに、まだこの時点では「超並列に適したプロセッサー」なるもののアーキテクチャーとはどんなものかに関しても理論が固まっていたわけではない。

インテルは80386やi860でそのままトーラスを構成したし、nCubeは独自とはいえ、プロセッサー部はごく普通の構成だ。コネクションマシーンは超並列の極北ともいえる1bitプロセッサーの集合体の構造だが、CM-2では32bit FPUノードを追加、CM-5ではSPARCを使ったりしているため、アーキテクチャー的には迷走しているとも言えなくもない。

そもそものT3Dの目的が超並列のアーキテクチャーの実装(特にソフトウェア面での対応)が主であり、プロセッサーそのものは極端な話、入手性が良く性能が出て実装密度が上げられるものだったらなんでもよかったと思われる。

汎用CPUのAlpha EV4は、以前ASCI Qの回で説明したが、浮動小数点演算性能はそう悪くなく、あとは適切なOSやコンパイラが用意されればそれなりの性能が発揮できると期待された。

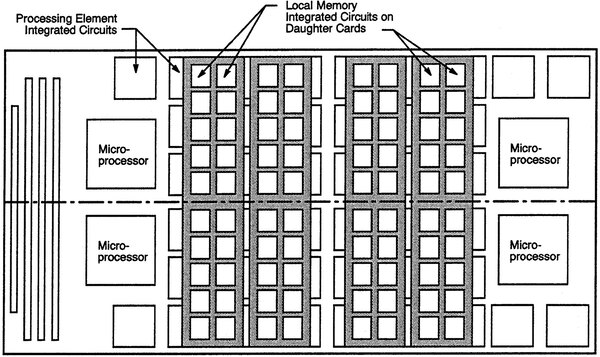

実装は、下の画像のように2 PE Node(つまり4PE)が1枚のボードの上に実装される構造になっていた。

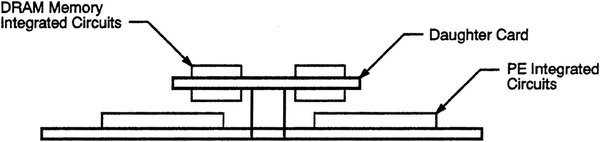

DRAMは下の画像のように、ボードの上にドーターカードを装着、ここに実装という仕組みである。

ところで先ほど3DトーラスでZ軸が2ノードしかないと述べたが、どうもT3Dの場合、Z軸方向のリンクはこのボードの上で完結していて外に出ない構造になっているように思える。

拡張性を無視すれば確かにこの実装はボード間配線も減らせるし良いアイディアであるが、ある程度ノード数が増えると通信のHop数が増えることになり、むしろ性能面ではネガティブになりかねない。最初の試みだから、そのあたりは控えめに実装を考えたのかもしれない。

ちなみにOSは、それまでCRAYで利用されていたUNICOSとは異なる、MicrokernelベースのものをUNICOS MAXという名前で実装した。

これは本当にタスクスケジューリングその他の機能しかないもので、フロントエンドにCRAYのC90などのマシンを用意し、ここがプログラムのロードやI/O処理などをつかさどる格好になった。その意味では、CRAY T3Dは巨大な超並列方式のアクセラレーターと言えなくもない。

このCRAY T3Dは1993年9月2日にプロトタイプがピッツバーグスーパーコンピュータセンターに納入された。この時点ではわずかに16PE Nodes(32プロセッサー)構成のものだが、19994年の初めには256PE Nodes(512プロセッサー)構成にアップグレードされ、ピーク性能で75GFLOPSを発揮することが期待された。

もっともこの納入の時のプレスリリースを見ると、同時にPSCはCRIとの間でソフトウェアの共同開発を行なう契約を結んだ、という話が出てきているあたり、ボトルネックがソフトウェアにあった事は明白である。

実際TOP500のスコアを見ると、EPFL(Ecole Polytechnique Federale de Lausanne:スイス連邦工科大学ローザンヌ校)に納入された128PE NodesのCRAY T3D MC256-8が理論性能38.40GFLOPSに対して実効性能は25.30GFLOPSである。

ピッツバーグスーパーコンピュータセンターの256 PE NodesのCRAY T3D MC512-8が理論性能76.80GFLOPSに対して実効性能50.80GFLOPSということで、効率は65~66%というあたりであまり褒められた数字ではない。とはいえ、ここで得た経験は次のT3Eに生かされることになった。

→次のページヘ続く (使える超並列マシン「CRAY T3E」)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ