1週空いたが、バス技術について解説する4回目は、最近まで主流だった「PCI」系列をまとめて説明しよう。

インテル主導で作られたPCI Bus

規格化時期も商品戦略に左右される?

連載107回でも説明したとおり、EISAは当初期待されたほどは普及せず、また性能的にも不十分であった。その一方で、VL-Busは広く普及して性能も高かったものの安定性に著しく欠けており、長期的に使い続けるのは難しい状態だった。もっとも、こうなる可能性は当初からある程度予期されていた。

インテルはこうしたことに備えており、1990年ころから「ADL」(Architecture Development Lab。後にIntel Architecture Labに改称)で新しいバスを開発して、1991年に「Local Glueless Bus」として業界に提案した。Microchannel(MCA)での失敗を目の当たりにしていたためか、インテルはLocal Glueless Busを特許やライセンスで保護することはせずに、業界標準規格として提案した。

PCI規格化のために1992年に設立されたのが、「PCI-SIG」(Peripheral Component Interconnect Special Interest Group)である。以後の標準化作業はPCI-SIGに移管され、インテルのみならず主要な業界各社を交えて、仕様策定が進められることになった。

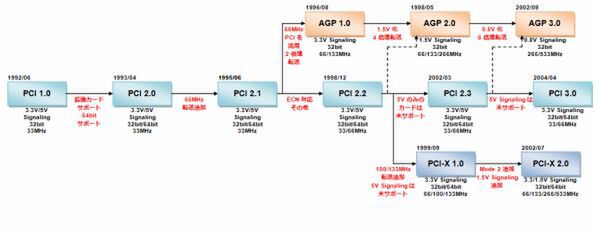

その最初の成果が、1992年6月に策定された「PCI Local Bus Revision 1.0」である。ちなみに本文では「PCI Bus」と表記しているが、正式な名称は最終版となるRevision 3.0まで、すべて「PCI Local Bus」である。

さてこのPCI 1.0だが、実は発表時点ではまだマザーボード上の内部バス、つまりチップセットと周辺回路などをつなぐバスとしてしか利用できず、拡張カードの仕様などは一切定まっていなかった。これらが定まるのは、翌1993年にリリースされた「Revision 2.0」からである。「どうせ10ヵ月なのだから、そこまで待てばいいのに」と思わなくもないのだが、このあたりの事情は製品動向に密接に関係していた。

インテルは1993年3月に、初のPCI対応チップセットである「Intel 430LX」をリリースした(関連記事)。だが、もしPCIの策定が1993年4月まで伸びていたら、このチップセットの投入が遅れることになってしまう。もちろん430LXには、PCI 2.0で策定されたものと「ほぼ同じ」拡張スロットを搭載していたし、バスプロトコルも一応PCI 2.0に「かなり近い」ものになっていた。それでも430LXそのものは「Revision 1.0準拠のPCI Busを搭載」となっており、実際1993年~1994年に市場投入されたPCIの拡張カードの中には動作しないものがあったりしたのは、致し方ないところか。

先に「主要な業界各社を交えて」とは書いたものの、その中でインテルが一番存在感が大きいのは間違いない。また標準化策定作業への貢献度も一番大きいわけだから、結果としてインテルチップセットにあわせるような標準化を急ぐ結果になったのも不思議ではない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ