信号電圧は5Vと3.3Vが併存

PCI Busそのものについて、簡単におさらいしておこう。まずバスの形式は、ISAやEISAと同じく共有バス方式のパラレル転送である。PCI 1.0時点での仕様は、バス幅は32bitでアドレス空間も32bit。信号速度は「最高」で33MHzである。最低は「0」なので、要するに33MHz以下であれば基本的には何でもOKである。実際、初期の製品の中には25MHzで駆動されるものもあった。

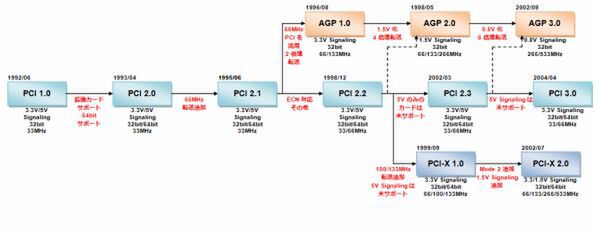

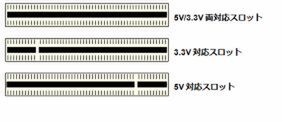

信号電圧は5Vと3.3Vの両方がサポートされている。拡張スロットが規定されていない1.0の時点では、オンボードデバイスだけだったからこれでも良かった。だがRevision 2.0で拡張スロットが定義されるにあたっては、混乱を招かないように「サポートするのが3.3Vか5Vか」は、スロットやカードエッジの形状でそれがわかるようになっている。

まずスロットの方は図1のようになっており、マザーボードがどちらの信号を扱えるかで形状が異なっている。これに対応する拡張カード側のカードエッジも図2のようになっている。実際筆者が所有していた当時の拡張カードを調べてみると、5V専用カードと両対応カードが結構入り乱れている。大雑把に言えば、2000年頃までのカードは圧倒的に5Vのみのものが多いが、それを過ぎると両対応製品がかなり多くなってきている。

発表当初は使えるものではなかったPCIだが、1993年に登場したRevision 2.0で拡張カードがサポートされるようになり、また32bit幅に加えて64bit幅も規定された。こちらはEISAなどと異なり、物理的にスロットの長さが長くなっている(XT-Bus→ISA Busの関係に近い)。バス幅の64bit化にあわせて、(オプションながら)64bitアドレスもここで定義されている。

このPCI 2.0に66MHz転送モードを追加したのが、1995年6月にリリースされた「Revision 2.1」である。このRevision 2.1は、インテルのIntel 440BXチップセットという大ヒットチップセットで実装されたRevisionでもあり、大きく普及することになった。この頃から拡張カードは、ISAに代わってPCIを使うようになり始めており、そうした普及に一役かったRevisionである。この2.1では、「Delayed Transaction」と呼ばれる転送効率向上のメカニズムのほか、PCI Bus ブリッジの定義なども追加されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ